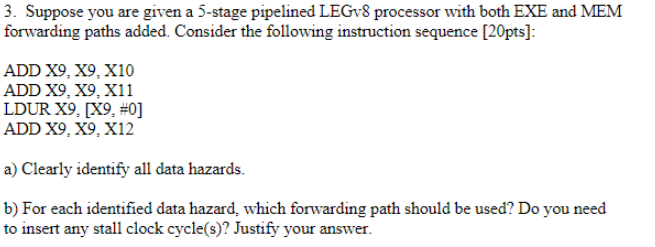

Question: 3. Suppose you are given a 5-stage pipelined LEGv8 processor with both EXE and MEM forwarding paths added. Consider the following instruction sequence [20pts] ADD

3. Suppose you are given a 5-stage pipelined LEGv8 processor with both EXE and MEM forwarding paths added. Consider the following instruction sequence [20pts] ADD X9, X9, X10 ADD X9, X9. X11 ADD X9, X9, X12 a) Clearly identify all data hazards. b) For each identified data hazard, which forwarding path should be used? Do you need to insert any stall clock cycle(s)? Justify your answer. 3. Suppose you are given a 5-stage pipelined LEGv8 processor with both EXE and MEM forwarding paths added. Consider the following instruction sequence [20pts] ADD X9, X9, X10 ADD X9, X9. X11 ADD X9, X9, X12 a) Clearly identify all data hazards. b) For each identified data hazard, which forwarding path should be used? Do you need to insert any stall clock cycle(s)? Justify your

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts