Question: 3. Understanding performance a) Assume that you are moving from a single-cycle MIPS processor design with frequency F and CPI Cbase to a 5-stage MIPS

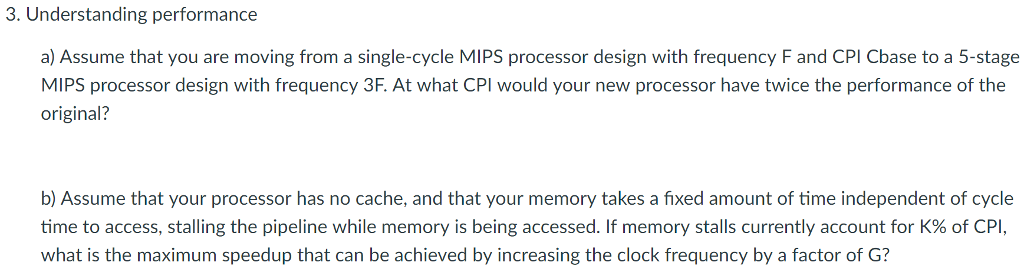

3. Understanding performance a) Assume that you are moving from a single-cycle MIPS processor design with frequency F and CPI Cbase to a 5-stage MIPS processor design with frequency 3F. At what CPI would your new processor have twice the performance of the original? b) Assume that your processor has no cache, and that your memory takes a fixed amount of time independent of cycle time to access, stalling the pipeline while memory is being accessed. If memory stalls currently account for 4% of CPI, what is the maximum speedup that can be achieved by increasing the clock frequency by a factor of G

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock