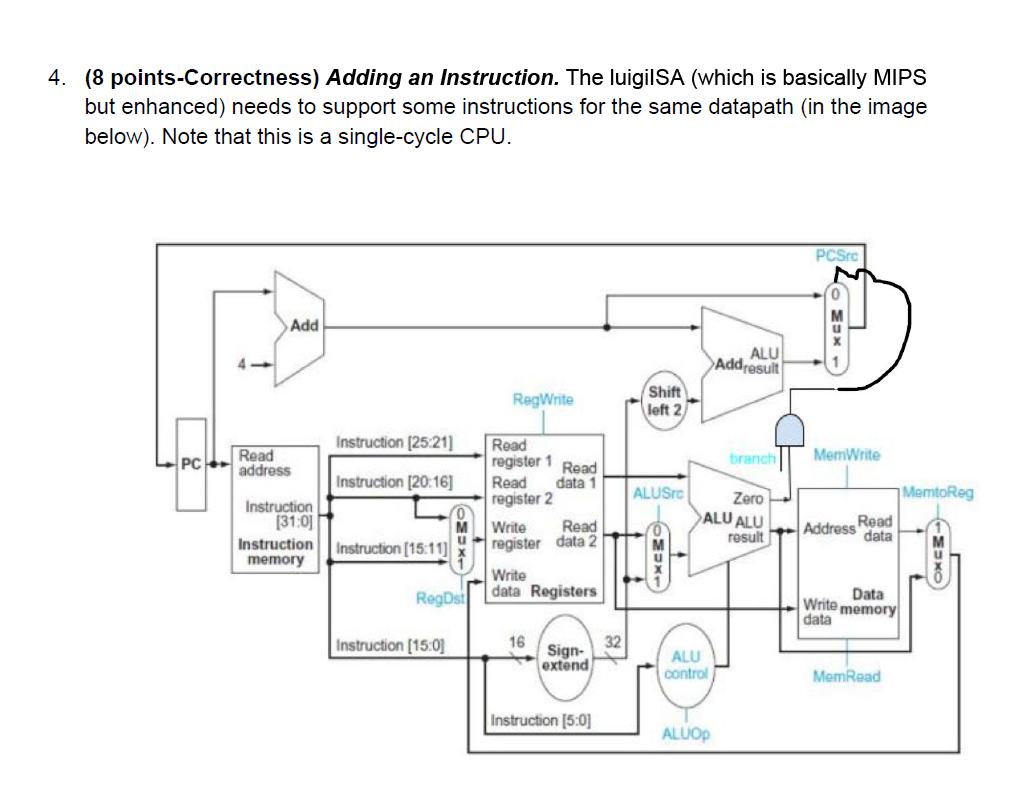

Question: 4. (8 points-Correctness) Adding an Instruction. The luigilSA (which is basically MIPS but enhanced) needs to support some instructions for the same datapath in the

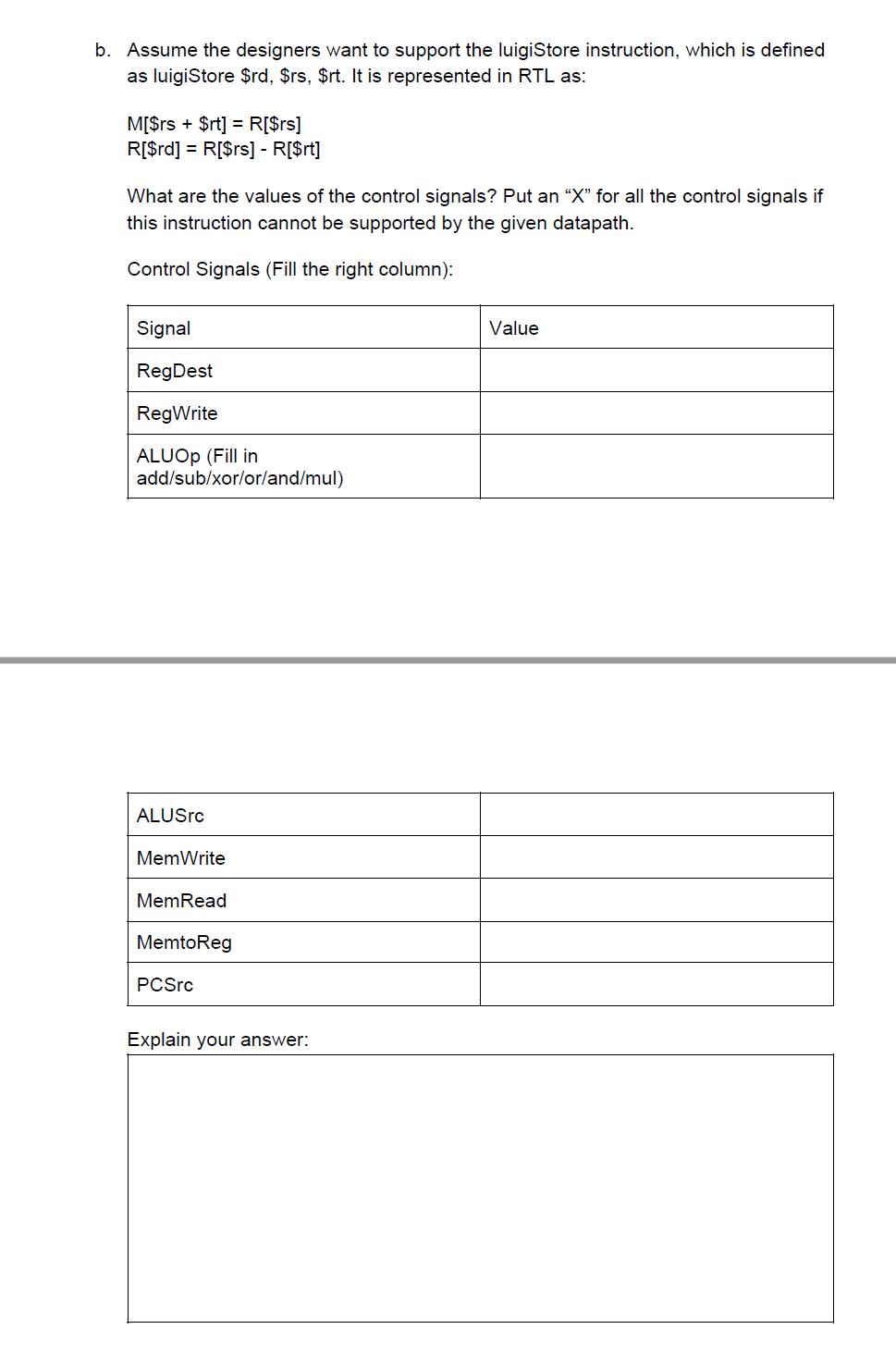

4. (8 points-Correctness) Adding an Instruction. The luigilSA (which is basically MIPS but enhanced) needs to support some instructions for the same datapath in the image below). Note that this is a single-cycle CPU. PCS > Add ALU Addresult RegWrite Shift left 2 branch MemWrite Instruction (25:21) Read address Instruction [2016] Instruction 0 [31:0) Instruction Instruction (15:11) memory Read register 1 Read Read data 1 register 2 Write Read register data 2 ALUSTO Zero MemtoReg Read ALU ALU Address data result U X Write data Registers exo) RegDst Data Write memory data Instruction (15:0) 16 32 Sign- extend ALU control MemRead Instruction (5:0) ALLOP b. Assume the designers want to support the luigiStore instruction, which is defined as luigiStore $rd, $rs, $rt. It is represented in RTL as: M[$rs + $rt] = R[$rs] R[$rd] = R[$rs] - R[$rt] What are the values of the control signals? Put an X for all the control signals if this instruction cannot be supported by the given datapath. Control Signals (Fill the right column): Signal Value RegDest RegWrite ALUOP (Fill in add/sub/xor/or/and/ mul) ALUSrc Mem Write MemRead MemtoReg PCSrc Explain your answer: 4. (8 points-Correctness) Adding an Instruction. The luigilSA (which is basically MIPS but enhanced) needs to support some instructions for the same datapath in the image below). Note that this is a single-cycle CPU. PCS > Add ALU Addresult RegWrite Shift left 2 branch MemWrite Instruction (25:21) Read address Instruction [2016] Instruction 0 [31:0) Instruction Instruction (15:11) memory Read register 1 Read Read data 1 register 2 Write Read register data 2 ALUSTO Zero MemtoReg Read ALU ALU Address data result U X Write data Registers exo) RegDst Data Write memory data Instruction (15:0) 16 32 Sign- extend ALU control MemRead Instruction (5:0) ALLOP b. Assume the designers want to support the luigiStore instruction, which is defined as luigiStore $rd, $rs, $rt. It is represented in RTL as: M[$rs + $rt] = R[$rs] R[$rd] = R[$rs] - R[$rt] What are the values of the control signals? Put an X for all the control signals if this instruction cannot be supported by the given datapath. Control Signals (Fill the right column): Signal Value RegDest RegWrite ALUOP (Fill in add/sub/xor/or/and/ mul) ALUSrc Mem Write MemRead MemtoReg PCSrc Explain your

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts