Question: 4 . For the unsigned addition of the given bit - pattern pair, identify the overall delay ( e . the delay at which all

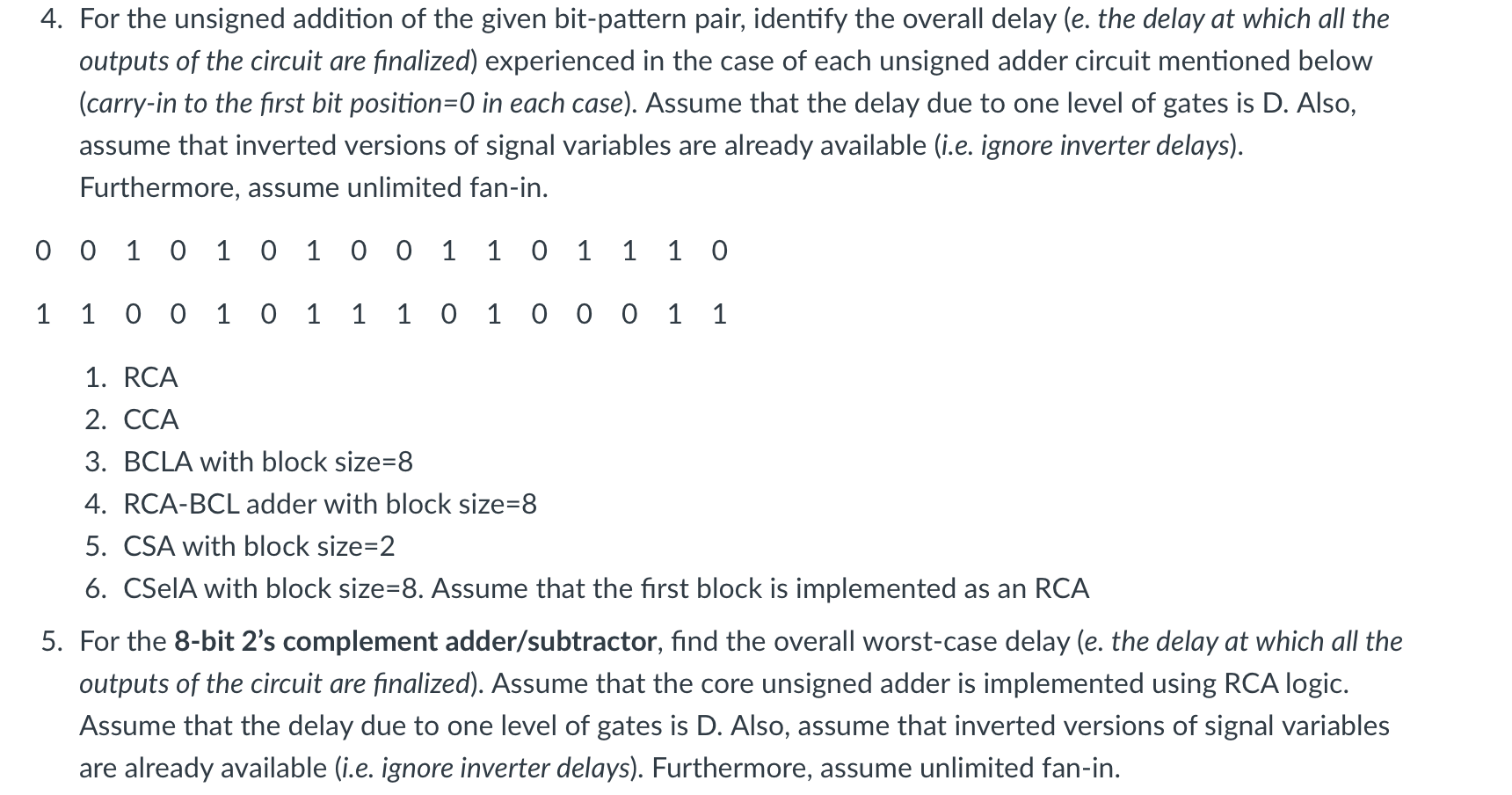

For the unsigned addition of the given bitpattern pair, identify the overall delay e the delay at which all the outputs of the circuit are finalized experienced in the case of each unsigned adder circuit mentioned below carryin to the first bit position in each case Assume that the delay due to one level of gates is D Also, assume that inverted versions of signal variables are already available ie ignore inverter delays Furthermore, assume unlimited fanin

beginarrayllllllllllllllll & & & & & & & & & & & & & & & endarray

RCA

CCA

BCLA with block size

RCABCL adder with block size

CSA with block size

CSelA with block size Assume that the first block is implemented as an RCA

For the bit s complement addersubtractor find the overall worstcase delay e the delay at which all the outputs of the circuit are finalized Assume that the core unsigned adder is implemented using RCA logic. Assume that the delay due to one level of gates is D Also, assume that inverted versions of signal variables are already available ie ignore inverter delays Furthermore, assume unlimited fanin

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock