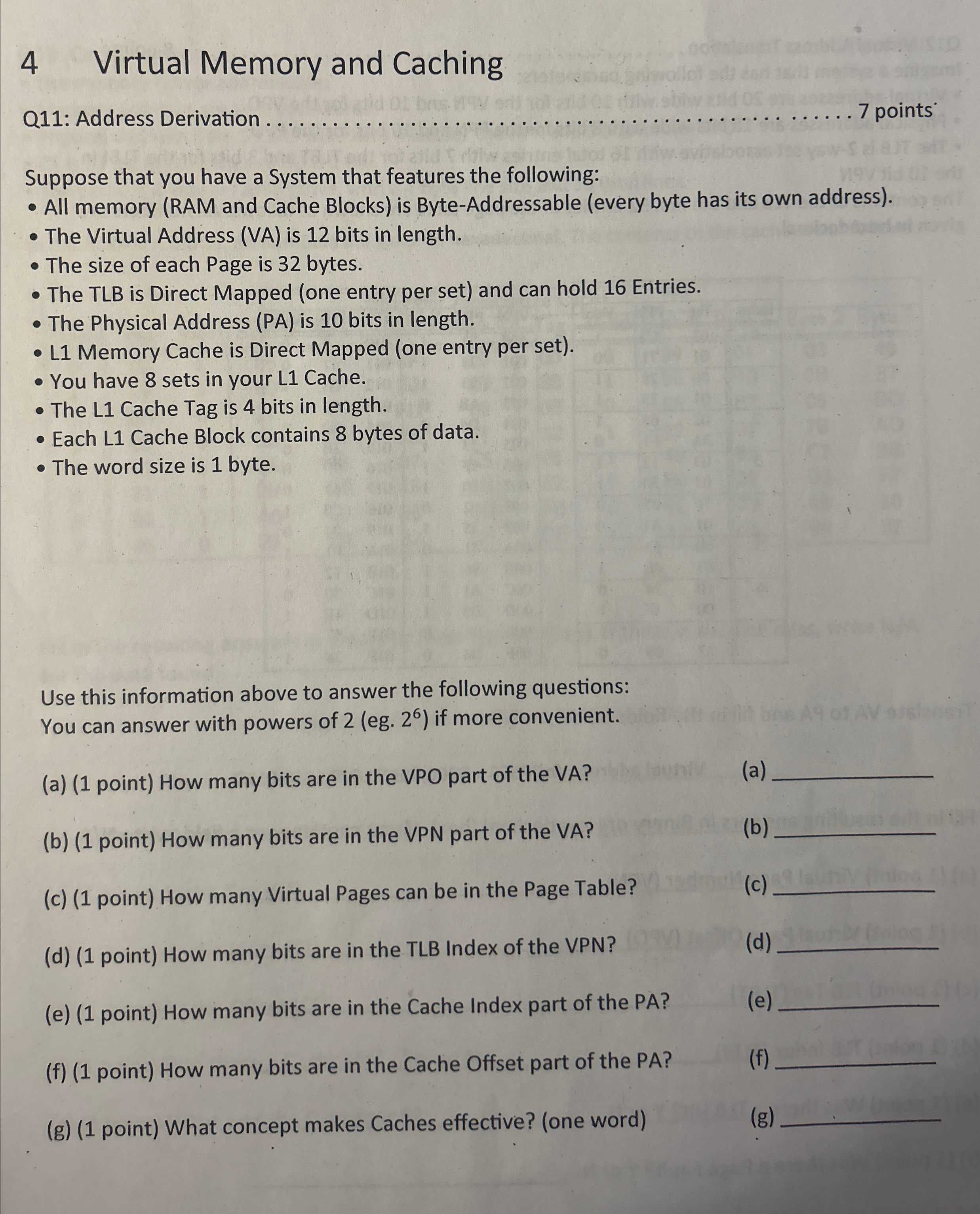

Question: 4 Virtual Memory and Caching Q 1 1 : Address Derivation q , q , q , q , q , q , q ,

Virtual Memory and Caching

Q: Address Derivation

Suppose that you have a System that features the following:

All memory RAM and Cache Blocks is ByteAddressable every byte has its own address

The Virtual Address VA is bits in length.

The size of each Page is bytes.

The TLB is Direct Mapped one entry per set and can hold Entries.

The Physical Address PA is bits in length.

L Memory Cache is Direct Mapped one entry per set

You have sets in your L Cache.

The L Cache Tag is bits in length.

Each L Cache Block contains bytes of data.

The word size is byte.

Use this information above to answer the following questions:

You can answer with powers of eg if more convenient.

a point How many bits are in the VPO part of the VA

a

b point How many bits are in the VPN part of the VA

b

c point How many Virtual Pages can be in the Page Table?

c

d point How many bits are in the TLB Index of the VPN

e point How many bits are in the Cache Index part of the PA

f point How many bits are in the Cache Offset part of the PA

f

g point What concept makes Caches effective? one word

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock