Question: 5.) The three circuits above would require 11 gates total. An equivalent circuit can be made more efficiently (I.E. using fewer gates). Design an equivalent

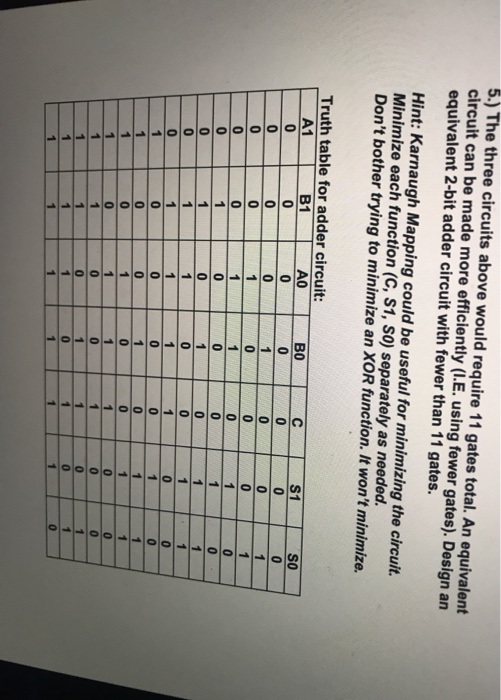

5.) The three circuits above would require 11 gates total. An equivalent circuit can be made more efficiently (I.E. using fewer gates). Design an equivalent 2-bit adder circuit with fewer than 11 gates. Hint: Karnaugh Mapping could be useful for minimizing the circuit. Minimize each function (C, S1, SO) separately as needed. Don't bother trying to minimize an XOR function. It won't minimize. Truth table for adder circuit: B1 AO A1 S1 10 C 0 0 0 0 0 OOOOOOO OO

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts