Question: 6. (10 marks) In this assignment you will design the top level instruction classifier, which is central to the instruction decoder in a MIPS processor.

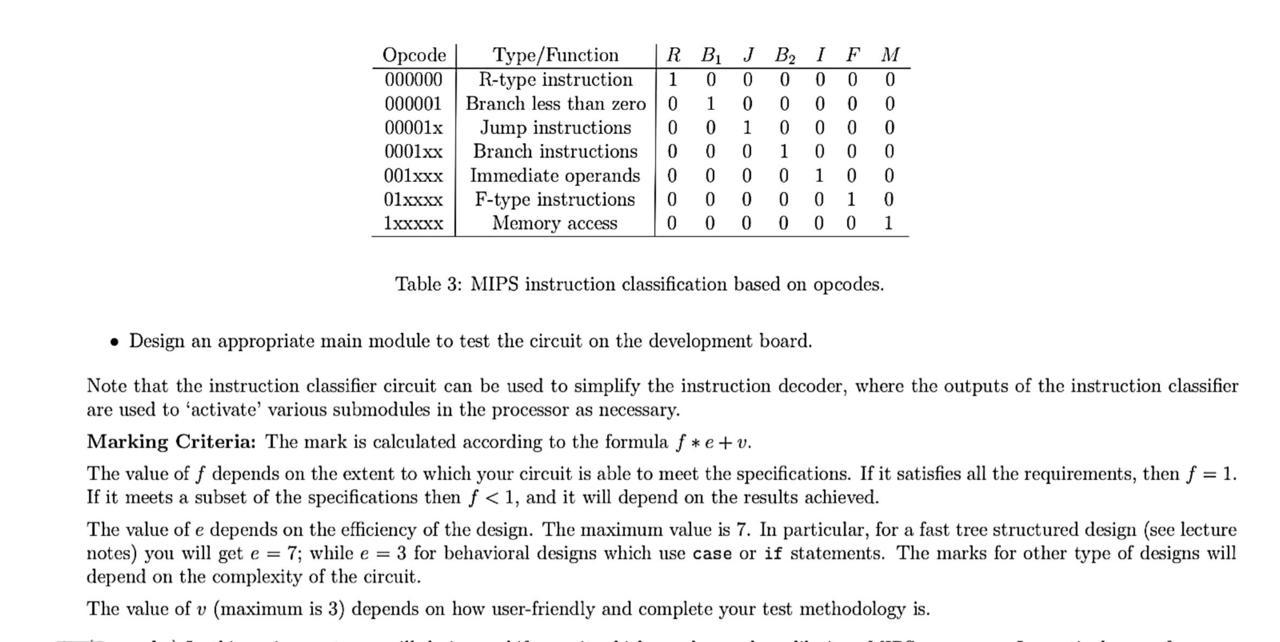

6. (10 marks) In this assignment you will design the top level instruction classifier, which is central to the instruction decoder in a MIPS processor. A MIPS instruction has a 6 bit "Opcode" input which determines what it is supposed to do. This module has 7 single-bit outputs R, B1, J, B2, 1, F, M. Table 3, which is an extract from the MIPS instruction set gives a summary of MIPS opcodes. The instruction classifier takes the opcode as input and asserts only one of the 7 output lines R, B1, J, B2, I, F and M as shown in Table 3 Design the instruction classifier as per Table 2 CSSsenam intretien position as selline Scanner J 0 Opcode 000000 000001 00001x 0001xx 001xxx 01xxxx 1xxxxx 0 1 Type/Function R-type instruction Branch less than zero Jump instructions Branch instructions Immediate operands F-type instructions Memory access RB 1 0 0 1 0 0 0 0 B2 I F M 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 Table 3: MIPS instruction classification based on opcodes. Design an appropriate main module to test the circuit on the development board. Note that the instruction classifier circuit can be used to simplify the instruction decoder, where the outputs of the instruction classifier are used to 'activate' various submodules in the processor as necessary. Marking Criteria: The mark is calculated according to the formula f*e+v. The value of f depends on the extent to which your circuit is able to meet the specifications. If it satisfies all the requirements, then f = 1. If it meets a subset of the specifications then f

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts