Question: 6. Assume your 32-bit computer (memory address 32-bits) has 16-KB (only L1-data) direct mapped cache. If the cache line size is 64-Bytes how many bits

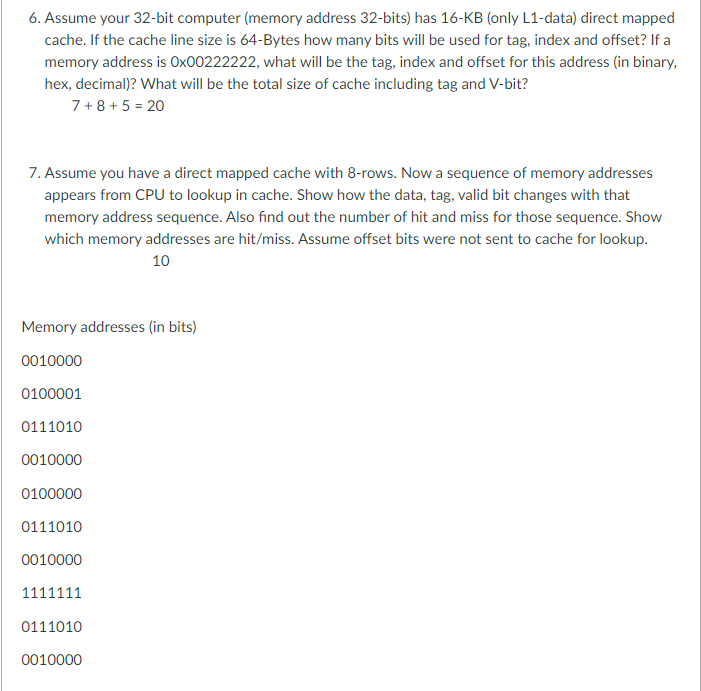

6. Assume your 32-bit computer (memory address 32-bits) has 16-KB (only L1-data) direct mapped cache. If the cache line size is 64-Bytes how many bits will be used for tag, index and offset? If a memory address is 0x00222222, what will be the tag, index and offset for this address (in binary, hex, decimal)? What will be the total size of cache including tag and V-bit? 7 + 8 + 5 = 20 7. Assume you have a direct mapped cache with 8-rows. Now a sequence of memory addresses appears from CPU to lookup in cache. Show how the data, tag, valid bit changes with that memory address sequence. Also find out the number of hit and miss for those sequence. Show which memory addresses are hit/miss. Assume offset bits were not sent to cache for lookup. 10 Memory addresses (in bits) 0010000 0100001 0111010 0010000 0100000 0111010 0010000 1111111 0111010 0010000

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts