Question: 6 . Consider the data - flow graph shown below: Assume the following parameter values for FPGA implementation: - Multiplication requires 5 0 clock cycles,

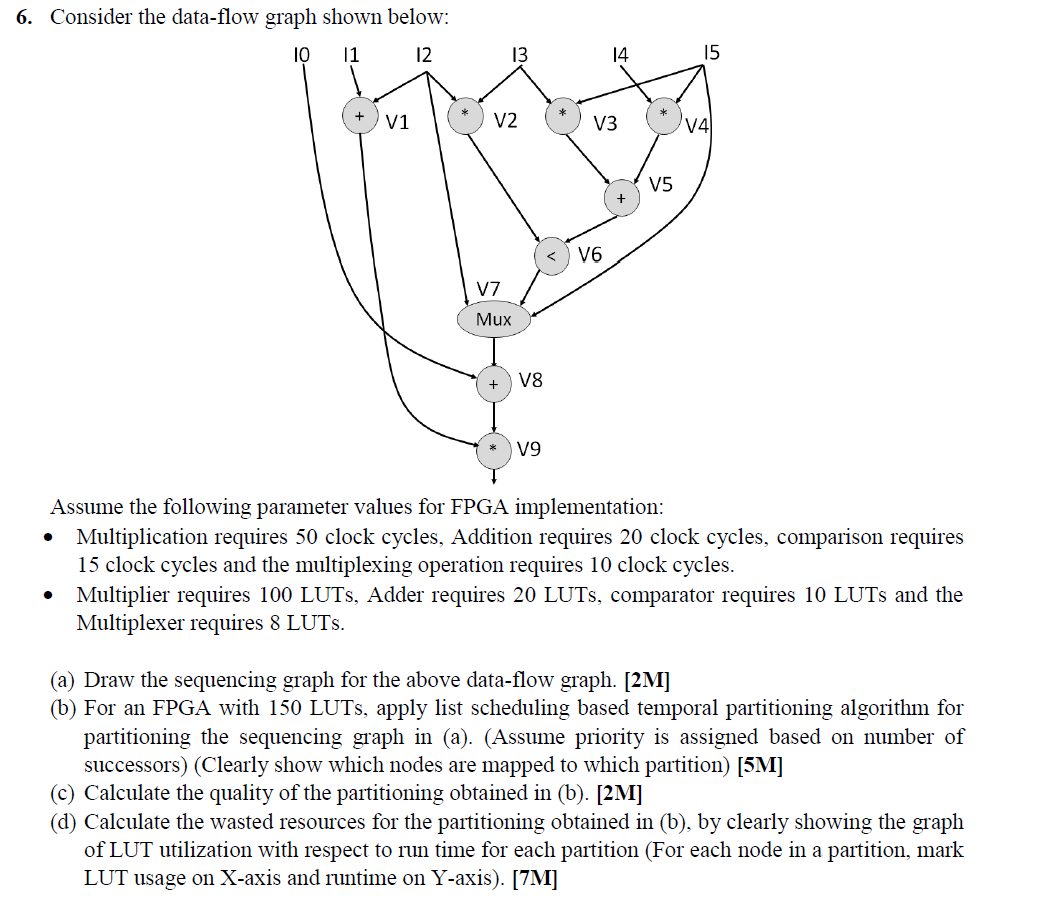

Consider the dataflow graph shown below:

Assume the following parameter values for FPGA implementation:

Multiplication requires clock cycles, Addition requires clock cycles, comparison requires clock cycles and the multiplexing operation requires clock cycles.

Multiplier requires LUTs, Adder requires LUTs, comparator requires LUTs and the Multiplexer requires LUTs.

a Draw the sequencing graph for the above dataflow graph. M

b For an FPGA with LUTs, apply list scheduling based temporal partitioning algorithm for partitioning the sequencing graph in aAssume priority is assigned based on number of successorsClearly show which nodes are mapped to which partitionM

c Calculate the quality of the partitioning obtained in bM

d Calculate the wasted resources for the partitioning obtained in b by clearly showing the graph of LUT utilization with respect to run time for each partition For each node in a partition, mark LUT usage on Xaxis and runtime on YaxisM

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock