Question: 6 . Problem 1 7 . 8 on page 6 5 2 . 1 7 . 8 a . Consider a uniprocessor with separate data

Problem on page

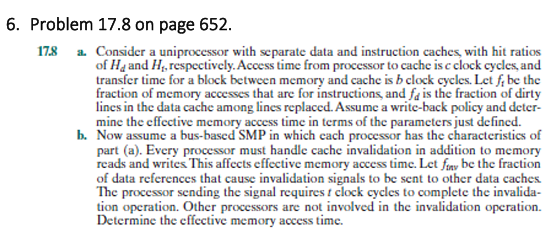

a Consider a uniprocessor with separate data and instruction caches, with hit ratios of Hd and Ht respectively. Access time from processor to cache is c clock cycles, and transfer time for a block between memory and cache is b clock cycles. Let fi be the fraction of memory accesses that are for instructions, and fd is the fraction of dirty lines in the data cache among lines replaced. Assume a writeback policy and determine the effective memory access time in terms of the parameters just defined.

b Now assume a busbased SMP in which each processor has the characteristics of part a Every processor must handle cache invalidation in addition to memory reads and writes This affects effective memory access time. Let ftext tny be the fraction of data references that cause invalidation signals to be sent to other data caches. The processor sending the signal requires t clock cycles to complete the invalidation operation. Other processors are not involved in the invalidation operation. Determine the effective memory access time.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock