Question: 7. (18 points) Circle T (true) or F (false) to indicate whether each statement below is true or false. All ARM instructions are 32 bits

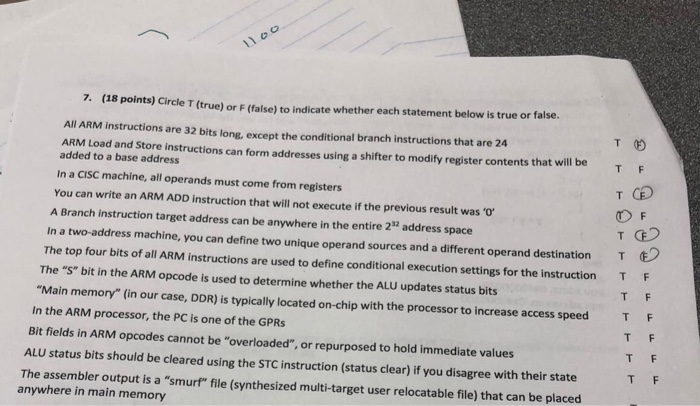

7. (18 points) Circle T (true) or F (false) to indicate whether each statement below is true or false. All ARM instructions are 32 bits long, except the conditional branch instructions that are 24 ARM Load and Store instructions can form addresses using a shifter to modify register contents that will be TF added to a base address In a CISC machine, all operands must come from registers You can write an ARM ADD instruction that will not execute if the previous result was A Branch instruction target address can be anywhere in the entire 2 address space In a two-address machine, you can define two unique operand sources and a different operand destination T The top four bits of all ARM instructions are used to define conditional execution settings for the instruction The "S" bit in the ARM opcode is used to determine whether the ALU updates status bits "Main memory" (in our case, DDR) is typically located on-chip with the processor to increase access speed In the ARM processor, the PC is one of the GPRS Bit fields in ARM opcodes cannot be "overloaded", or repurposed to hold immediate values T F T F ALU status bits should be cleared using the STC instruction (status clear) if you disagree with their state The assembler output is a "smurf" file (synthesized multi-target user relocatable file) that can be placed anywhere in main memory

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts