Question: 7) Problem 3.12 text 3.12 Trace the behavior of an edge-triggered D flip-flop using a master-servant design (see Figure 3.25) for the input pattern in

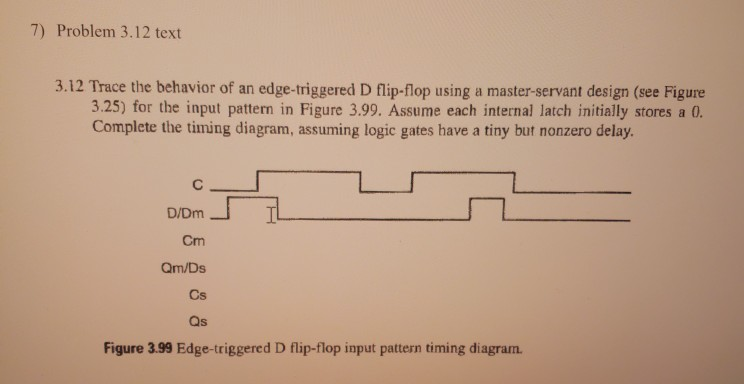

7) Problem 3.12 text 3.12 Trace the behavior of an edge-triggered D flip-flop using a master-servant design (see Figure 3.25) for the input pattern in Figure 3.99. Assume each internal latch initially stores a Complete the timing diagram, assuming logic gates have a tiny but nonzero delay D/Dm Cm Qm/Ds Cs Qs Figure 3.99 Edge-triggered D flip-flop input pattern timing diagram

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock