Question: 8) (20 points) Timing issues in shift registers. The propagation delay of a positive edge triggered D-type flip-flop is defined as the time delay between

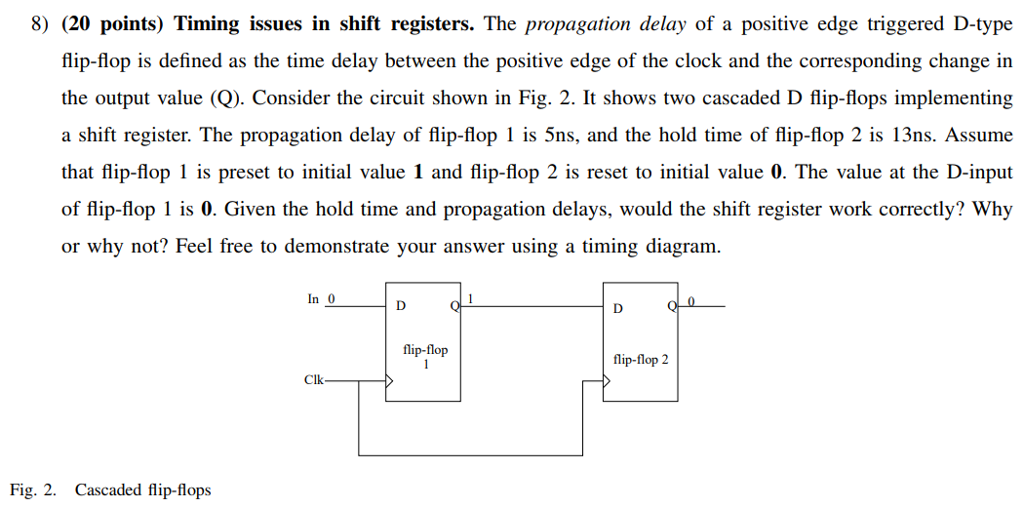

8) (20 points) Timing issues in shift registers. The propagation delay of a positive edge triggered D-type flip-flop is defined as the time delay between the positive edge of the clock and the corresponding change in the output value (Q). Consider the circuit shown in Fig. 2. It shows two cascaded D flip-flops implementing a shift register. The propagation delay of flip-flop 1 is 5ns, and the hold time of flip-flop 2 is 13ns. Assume that flip-flop 1 is preset to initial value 1 and flip-flop 2 is reset to initial value 0. The value at the D-input of flip-flop 1 is 0. Given the hold time and propagation delays, would the shift register work correctly? Why or why not? Feel free to demonstrate your answer using a timing diagram. DO flip-flop flip-flop 2 Clk Fig. 2. Cascaded flip-flops 8) (20 points) Timing issues in shift registers. The propagation delay of a positive edge triggered D-type flip-flop is defined as the time delay between the positive edge of the clock and the corresponding change in the output value (Q). Consider the circuit shown in Fig. 2. It shows two cascaded D flip-flops implementing a shift register. The propagation delay of flip-flop 1 is 5ns, and the hold time of flip-flop 2 is 13ns. Assume that flip-flop 1 is preset to initial value 1 and flip-flop 2 is reset to initial value 0. The value at the D-input of flip-flop 1 is 0. Given the hold time and propagation delays, would the shift register work correctly? Why or why not? Feel free to demonstrate your answer using a timing diagram. DO flip-flop flip-flop 2 Clk Fig. 2. Cascaded flip-flops

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts