Question: 9. (10 pts) Consider the LEGv8 code below L1: ADD X3, X5, X3 LDUR X7, [X3, #4] ADD X2, X5, X7 SUB X4, X3, X7

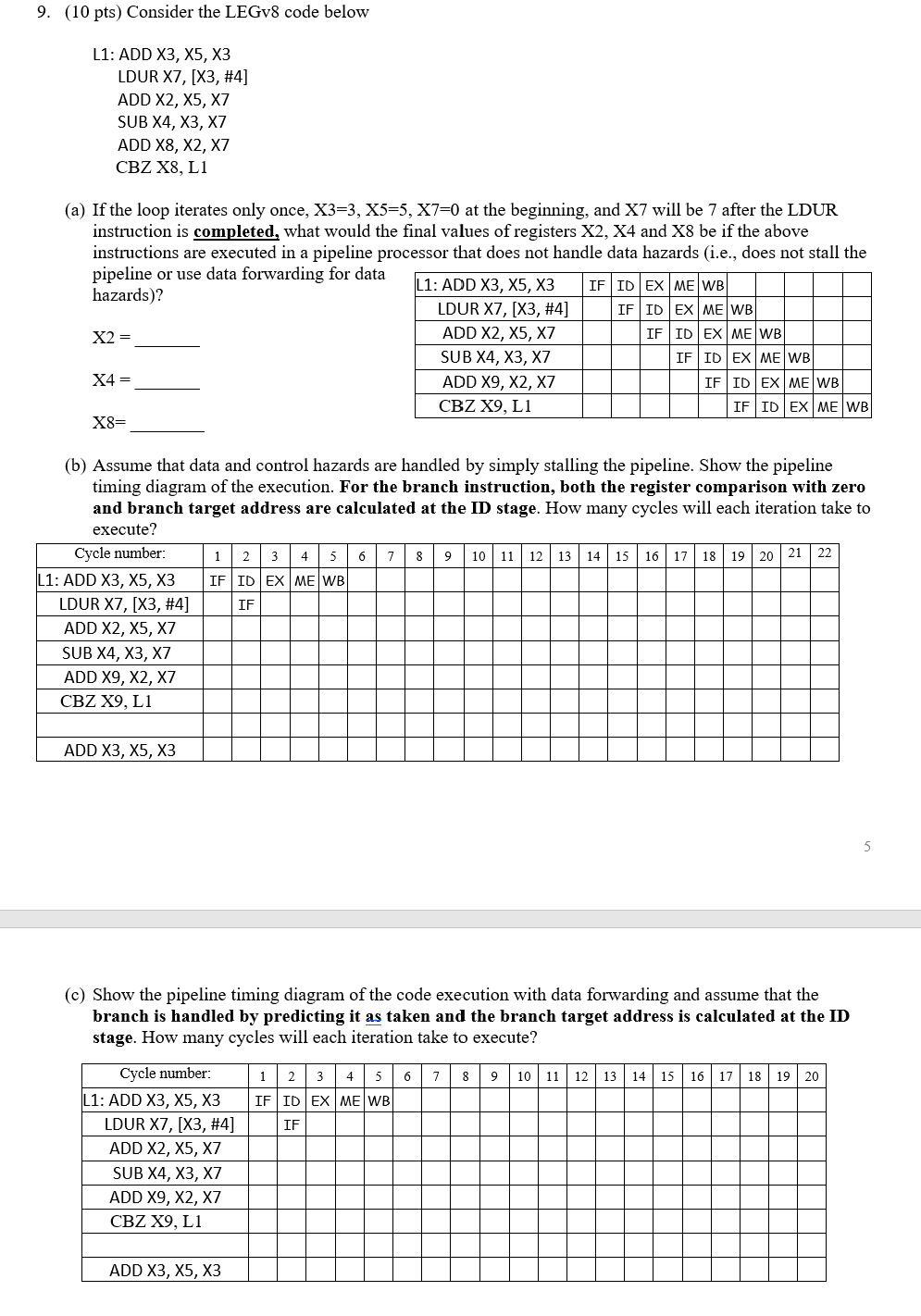

9. (10 pts) Consider the LEGv8 code below L1: ADD X3, X5, X3 LDUR X7, [X3, #4] ADD X2, X5, X7 SUB X4, X3, X7 ADD X8, X2, X7 CBZ X8, L1 (a) If the loop iterates only once, X3=3, X5=5, X7=0 at the beginning, and X7 will be 7 after the LDUR instruction is completed, what would the final values of registers X2, X4 and X8 be if the above instructions are executed in a pipeline processor that does not handle data hazards (i.e., does not stall the pipeline or use data forwarding for data L1: ADD X3, X5, X3 IF ID EX ME WB hazards)? LDUR X7, [X3, #4] IF ID EX ME WB X2 = ADD X2, X5, X7 IF ID EX MEWB SUB X4, X3, X7 IF ID EX ME WB X4= ADD X9, X2, X7 IF ID EX ME WB CBZ X9, L1 IF IDEX MEWB X8= 1 3 5 6 7 8 9 12 13 22 (b) Assume that data and control hazards are handled by simply stalling the pipeline. Show the pipeline timing diagram of the execution. For the branch instruction, both the register comparison with zero and branch target address are calculated at the ID stage. How many cycles will each iteration take to execute? Cycle number: 2 4 10 11 14 | 15 16 17 18 19 20 21 L1: ADD X3, X5, X3 IF ID EX MEWB LDUR X7, [X3, #4] IF ADD X2, X5, X7 SUB X4, X3, X7 ADD X9, X2, X7 CBZ X9, L1 ADD X3, X5, X3 5 1 2 3 4 5 6 7 8 9 20 (c) Show the pipeline timing diagram of the code execution with data forwarding and assume that the branch is handled by predicting it as taken and the branch target address is calculated at the ID stage. How many cycles will each iteration take to execute? Cycle number: 10 11 12 13 14 15 16 17 18 19 L1: ADD X3, X5, X3 IF ID EX ME WB LDUR X7, [X3, #4] ADD X2, X5, X7 SUB X4, X3, X7 ADD X9, X2, X7 CBZ X9, L1 IF ADD X3, X5, X3

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts