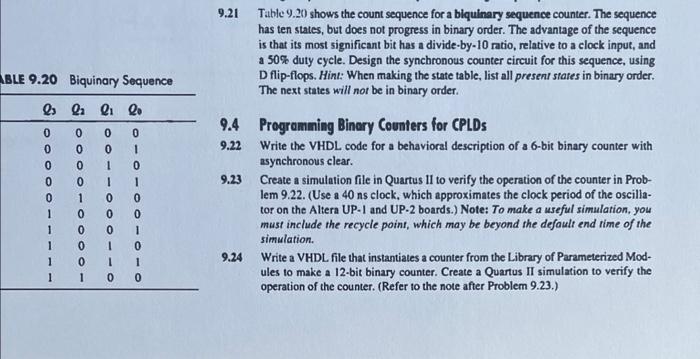

Question: 9.21 please 21 Table 9.20 shows the count sequence for a biquinary sequence counter. The sequence has ten states, but does not progress in binary

21 Table 9.20 shows the count sequence for a biquinary sequence counter. The sequence has ten states, but does not progress in binary order. The advantage of the sequence is that its most significant bit has a divide-by-10 ratio, relative to a clock input, and a 50% duty cycle. Design the synchronous counter circuit for this sequence, using D flip-flops. Hint: When making the state table, list all present states in binary order. The next states will not be in binary order. Progremming Binery Counters for CPLDs Write the VHDL code for a behavioral description of a 6-bit binary counter with asynchronous clear. 23 Create a simulation file in Quartus II to verify the operation of the counter in Problem 9.22. (Use a 40ns clock, which approximates the clock period of the oscillator on the Altera UP-I and UP-2 boards.) Note: To make a useful simulation, you must include the recycle point, which may be beyond the default end time of the simulation. 24. Write a VHDL file that instantiates a counter from the Library of Parameterized Modules to make a 12-bit binary counter. Create a Quartus II simulation to verify the operation of the counter. (Refer to the note after Problem 9.23.)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts