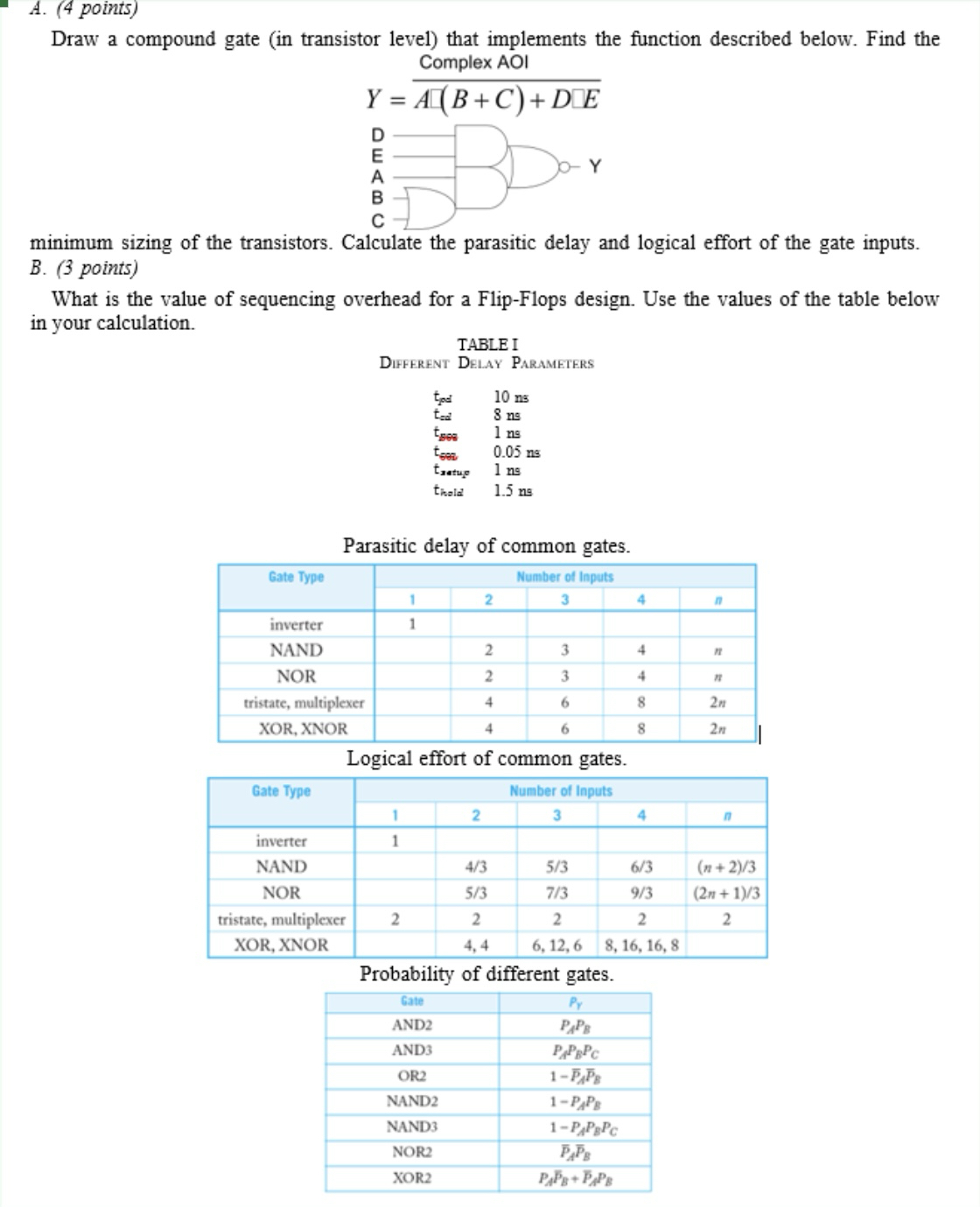

Question: A . ( 4 points ) Draw a compound gate ( in transistor level ) that implements the function described below. Find the Complex AOI

A points

Draw a compound gate in transistor level that implements the function described below. Find the Complex AOI

minimum sizing of the transistors. Calculate the parasitic delay and logical effort of the gate inputs.

B points

What is the value of sequencing overhead for a FlipFlops design. Use the values of the table below in your calculation.

TABLE I

Different Delay Parameters

table ns ns ns ngtaetup ns n

Parasitic delay of common gates.

tableGate Type,Number of lnputs

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock