Question: a) A processor executes native instructions by using six basic operations of fetch, decode, execute, address-decode, memory access and write-back. Each of these operations

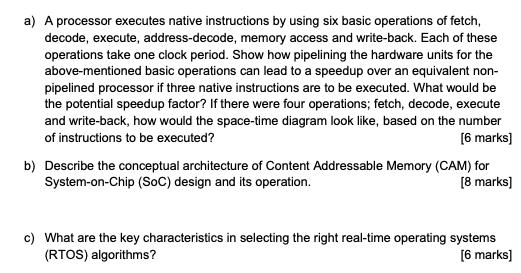

a) A processor executes native instructions by using six basic operations of fetch, decode, execute, address-decode, memory access and write-back. Each of these operations take one clock period. Show how pipelining the hardware units for the above-mentioned basic operations can lead to a speedup over an equivalent non- pipelined processor if three native instructions are to be executed. What would be the potential speedup factor? If there were four operations; fetch, decode, execute and write-back, how would the space-time diagram look like, based on the number of instructions to be executed? [6 marks] b) Describe the conceptual architecture of Content Addressable Memory (CAM) for System-on-Chip (SoC) design and its operation. [8 marks] c) What are the key characteristics in selecting the right real-time operating systems (RTOS) algorithms? [6 marks]

Step by Step Solution

There are 3 Steps involved in it

The image contains three questions related to computer architecture and operating systems Each question requires an indepth response Ill explain each part one by one a In a processor the execution of ... View full answer

Get step-by-step solutions from verified subject matter experts