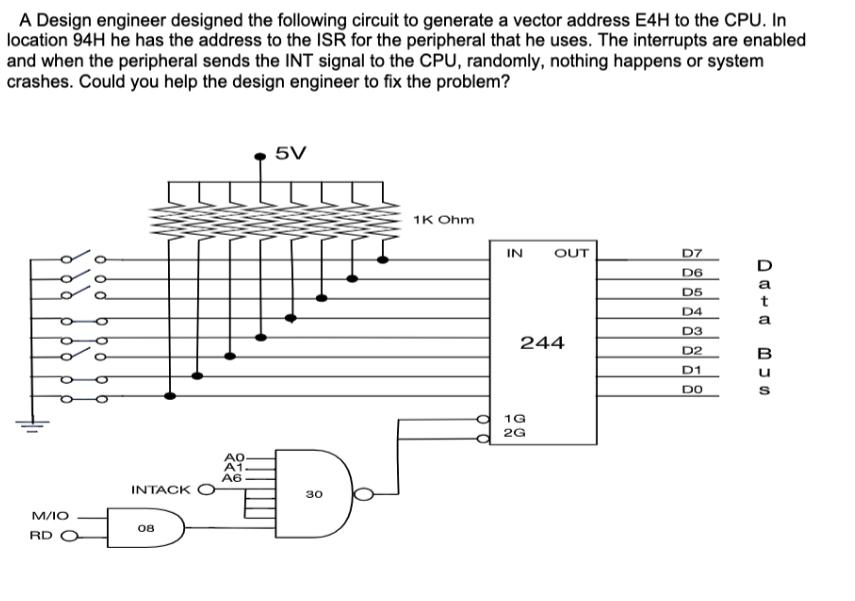

Question: A Design engineer designed the following circuit to generate a vector address E4H to the CPU. In location 94H he has the address to

A Design engineer designed the following circuit to generate a vector address E4H to the CPU. In location 94H he has the address to the ISR for the peripheral that he uses. The interrupts are enabled and when the peripheral sends the INT signal to the CPU, randomly, nothing happens or system crashes. Could you help the design engineer to fix the problem? 0 0 0 M/IO RD INTACK O 08 A1 A6 5V 30 1K ohm IN OUT 244 1G 2G D7 D6 D5 D4 D3 D2 D1 DO 9190 t a BUS

Step by Step Solution

3.39 Rating (149 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts