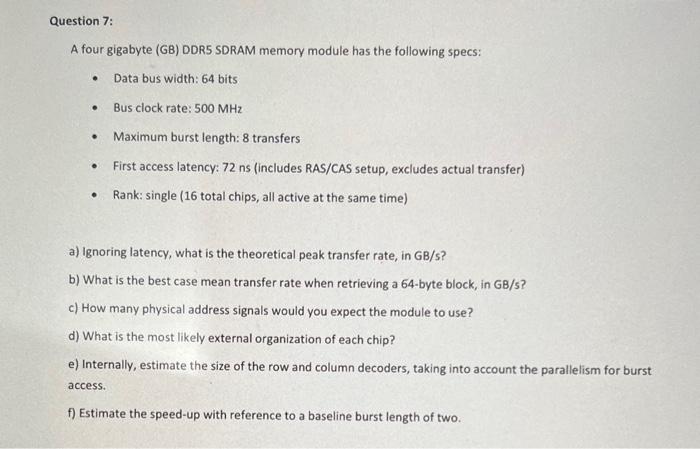

Question: A four gigabyte (GB) DDR5 SDRAM memory module has the following specs: - Data bus width: 64 bits - Bus clock rate: 500MHz - Maximum

A four gigabyte (GB) DDR5 SDRAM memory module has the following specs: - Data bus width: 64 bits - Bus clock rate: 500MHz - Maximum burst length: 8 transfers - First access latency: 72 ns (includes RAS/CAS setup, excludes actual transfer) - Rank: single (16 total chips, all active at the same time) a) Ignoring latency, what is the theoretical peak transfer rate, in GB/s ? b) What is the best case mean transfer rate when retrieving a 64 -byte block, in GB/5 ? c) How many physical address signals would you expect the module to use? d) What is the most likely external organization of each chip? e) Internally, estimate the size of the row and column decoders, taking into account the parallelism for burst access. f) Estimate the speed-up with reference to a baseline burst length of two

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts