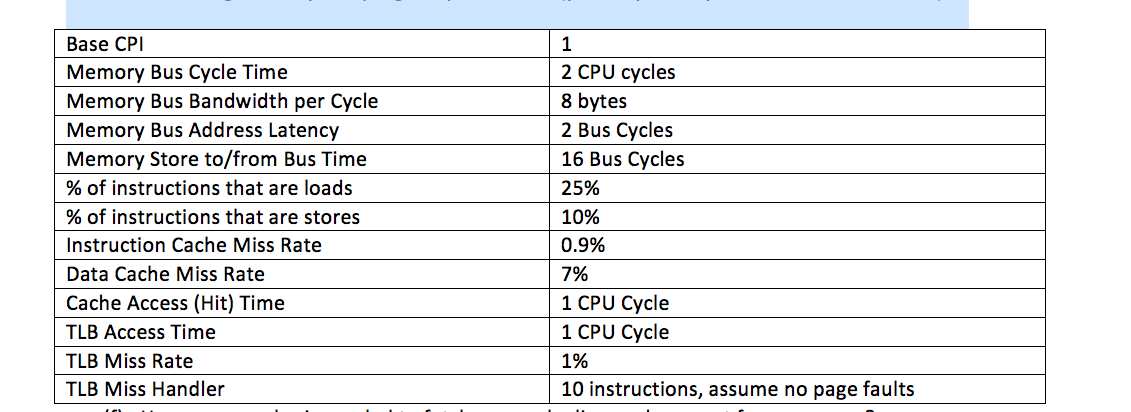

Question: a) How many cycles is needed to fetch one cache line replacement from memory? b) What is the average number of cycles needed to handle

a) How many cycles is needed to fetch one cache line replacement from memory?

b) What is the average number of cycles needed to handle one TLB miss?

c) What is the average memory access time (AMAT) for a data read if the cache is virtually addressed?

d) What is the AMAT for a data read if the cache is physically addressed?

e) What is the effective CPI if the data cache uses write-back, 30% of replaced data cache blocks are dirty, there is a write buffer that is never full, and both caches are virtually indexed-physically tagged?

What is the effective CPI if the data cache uses write-through and write-allocate with no write buffer, the instruction cache is virtually addressed, and the data cache is physically addressed?

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts