Question: A processor with a two - level cache hierarchy employs hardware prefetching to enhance performance. The L 1 and L 2 caches are 3 2

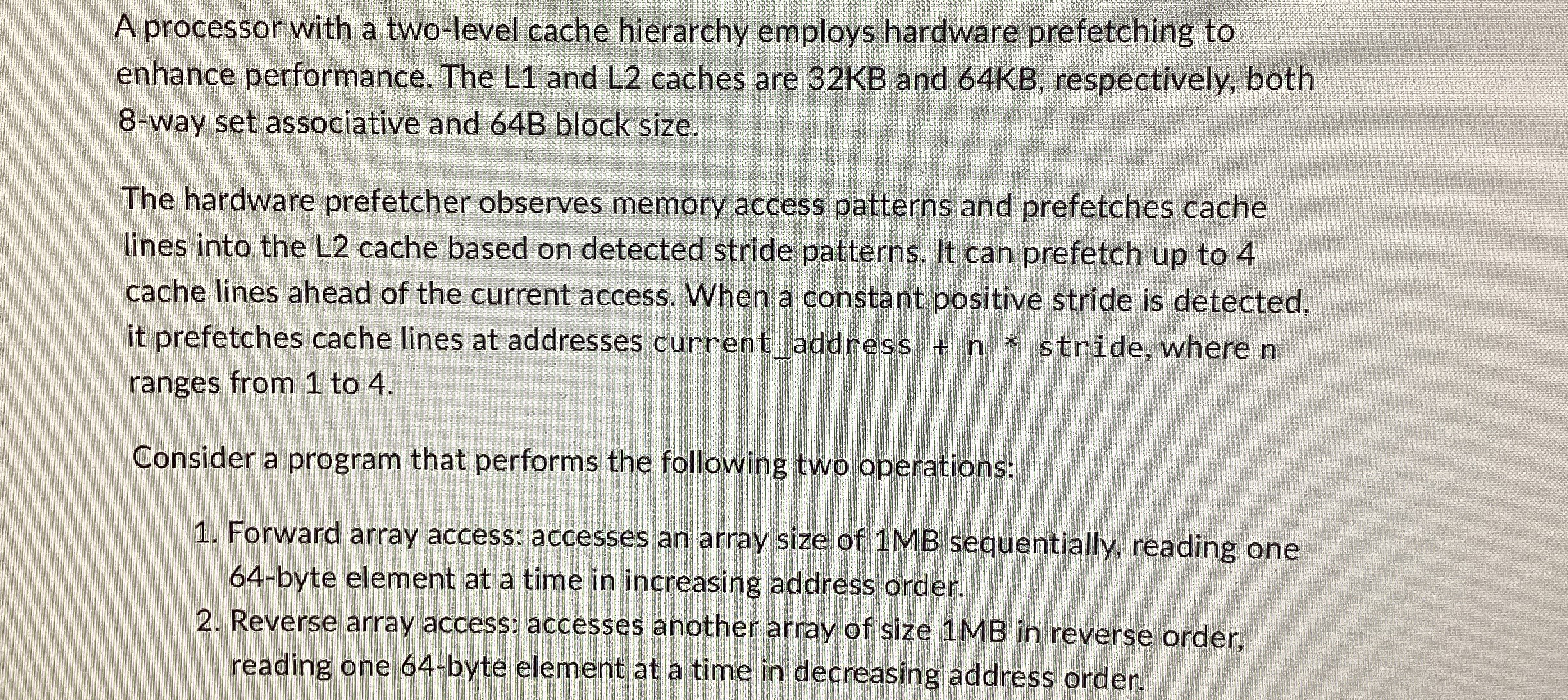

A processor with a twolevel cache hierarchy employs hardware prefetching to

enhance performance. The L and L caches are KB and KB respectively, both

way set associative and B block size.

The hardware prefetcher observes memory access patterns and prefetches cache

lines into the L cache based on detected stride patterns. It can prefetch up to

cache lines ahead of the current access. When a constant positive stride is detected,

it prefetches cache lines at addresses currentaddress stride, where

ranges from to

Consider a program that performs the following two operations:

Forward array access: accesses an array size of MB sequentially, reading one

byte element at a time in increasing address order.

Reverse array access: accesses another array of size MB in reverse order,

reading one byte element at a time in decreasing address order.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock