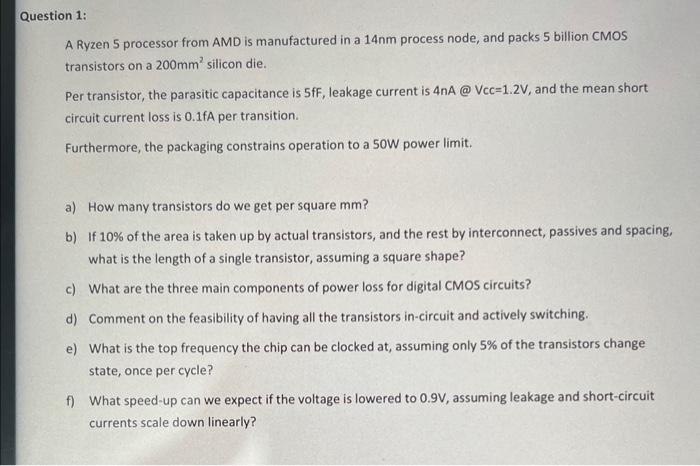

Question: A Ryzen 5 processor from AMD is manufactured in a 14nm process node, and packs 5 billion CMOS transistors on a 200mm2 silicon die. Per

A Ryzen 5 processor from AMD is manufactured in a 14nm process node, and packs 5 billion CMOS transistors on a 200mm2 silicon die. Per transistor, the parasitic capacitance is 5fF, leakage current is 4nA@Vcc=1.2V, and the mean short circuit current loss is 0.1 f A per transition. Furthermore, the packaging constrains operation to a 50W power limit. a) How many transistors do we get per square mm? b) If 10% of the area is taken up by actual transistors, and the rest by interconnect, passives and spacing, what is the length of a single transistor, assuming a square shape? c) What are the three main components of power loss for digital CMOS circuits? d) Comment on the feasibility of having all the transistors in-circuit and actively switching. e) What is the top frequency the chip can be clocked at, assuming only 5% of the transistors change state, once per cycle? f) What speed-up can we expect if the voltage is lowered to 0.9V, assuming leakage and short-circuit currents scale down linearly

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts