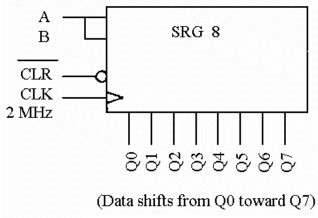

Question: A serial data path needs a 1000 ns delay. A shift-register with serial-in/ parallel-out is used for this purpose. Which output from the Shift-Register above

|

| A serial data path needs a 1000 ns delay. A shift-register with serial-in/ parallel-out is used for this purpose. Which output from the Shift-Register above will provide the correct output to extract the serial signal (correct delay)? Assume that the data is presented to the serial inputs right before the rising edge of the clock and also the propagation time of the internal flip-flops is very small. The clock frequency of the shift-register is 2MHz. |

| Q0 |

| Q1 |

| Q4 |

| None of the above |

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock