Question: A SMP system contains three processors with L2 caches connected using a time shared bus is shown in the figure 4B. Explain how the

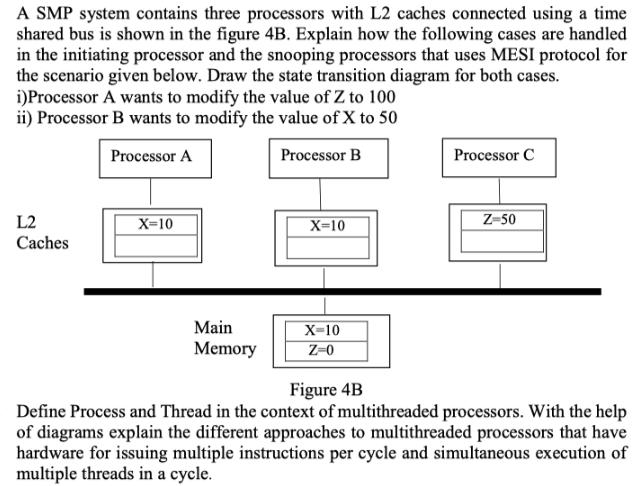

A SMP system contains three processors with L2 caches connected using a time shared bus is shown in the figure 4B. Explain how the following cases are handled in the initiating processor and the snooping processors that uses MESI protocol for the scenario given below. Draw the state transition diagram for both cases. i) Processor A wants to modify the value of Z to 100 ii) Processor B wants to modify the value of X to 50 Processor A Processor B L2 Caches X=10 Main Memory X-10 X=10 Z-0 Processor C Z-50 Figure 4B Define Process and Thread in the context of multithreaded processors. With the help of diagrams explain the different approaches to multithreaded processors that have hardware for issuing multiple instructions per cycle and simultaneous execution of multiple threads in a cycle.

Step by Step Solution

3.44 Rating (147 Votes )

There are 3 Steps involved in it

Question 1 The MESI protocol is a cache coherence protocol that uses four states to mark the status of each cache line Modified Exclusive Shared and Invalid 12 The protocol ensures that only one proce... View full answer

Get step-by-step solutions from verified subject matter experts