Question: A standard positive-edge trigger Flip-Flop (DFF) is provided as a building block. The goal is to add logic (AND. OR, INV, or MUX) to the

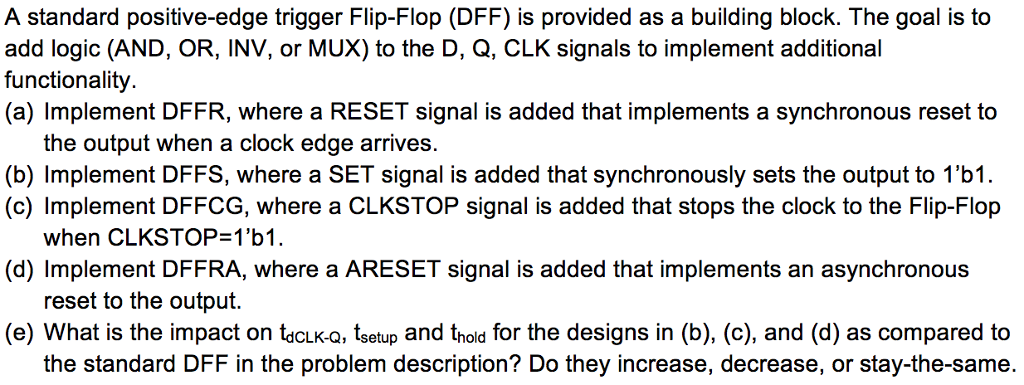

A standard positive-edge trigger Flip-Flop (DFF) is provided as a building block. The goal is to add logic (AND. OR, INV, or MUX) to the D, Q, CLK signals to implement additional functionality. (a) Implement DFFR, where a RESET signal is added that implements a synchronous reset to the output when a clock edge arrives. (b) Implement DFFS, where a SET signal is added that synchronously sets the output to 1b1. (c) Implement DFFCG, where a CLKSTOP signal is added that stops the clock to the Flip-Flop when CLKST0P = 1b1. (d) Implement DFFRA, where a ARESET signal is added that implements an asynchronous reset to the output. (e) What is the impact on t_dCLK-Q, t_setup and t_hold for the designs in (b), (c), and (d) as compared to the standard DFF in the problem description? Do they increase, decrease, or stay-the-same

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts