Question: Answer the cirlced questions please ( 1 . ) Draw a logic diagram constructing a 3 8 decoder with active - low enable, using a

Answer the cirlced questions please

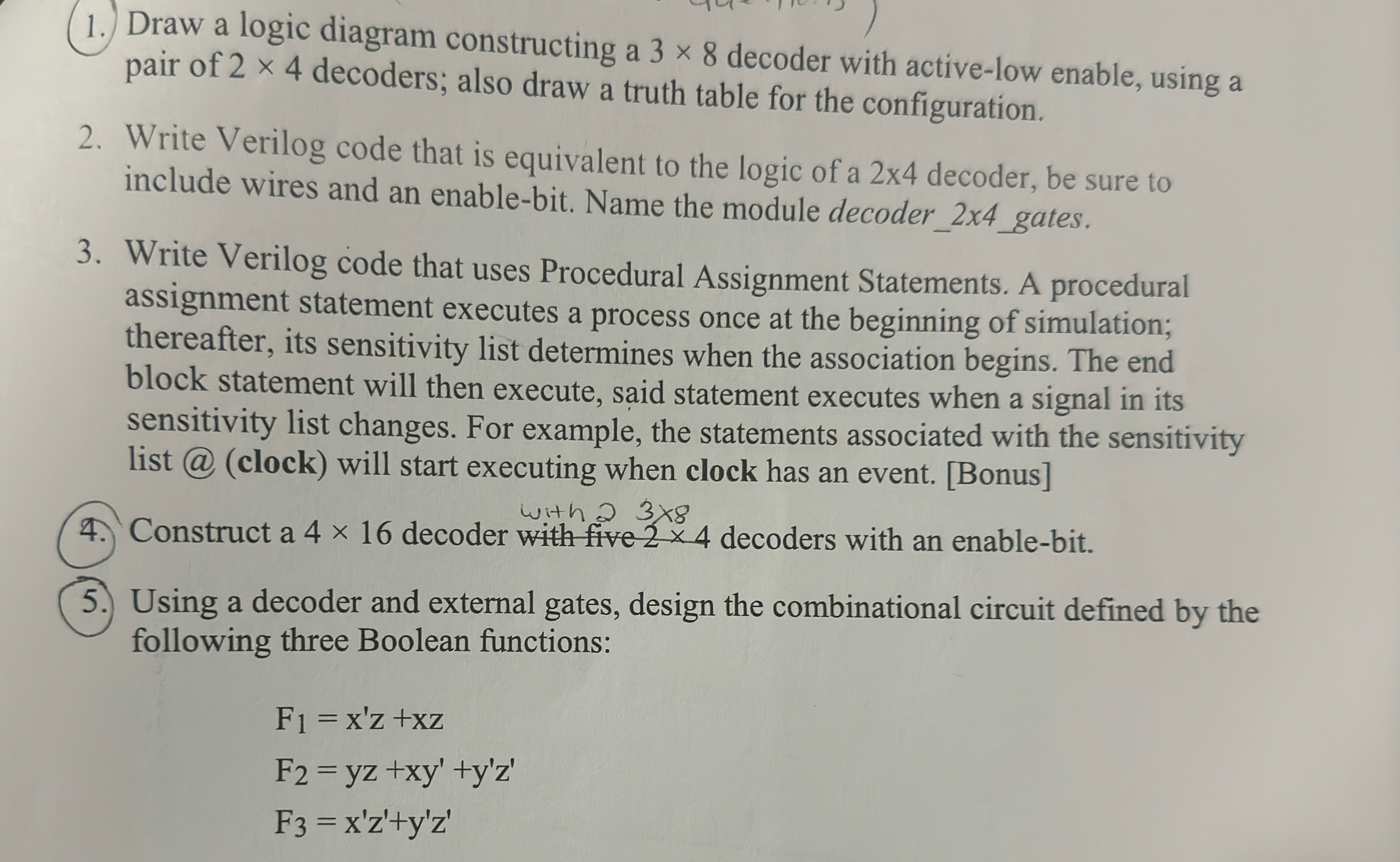

Draw a logic diagram constructing a decoder with activelow enable, using a pair of decoders; also draw a truth table for the configuration.

Write Verilog code that is equivalent to the logic of a decoder, be sure to include wires and an enablebit. Name the module decoderxgates.

Write Verilog code that uses Procedural Assignment Statements. A procedural assignment statement executes a process once at the beginning of simulation; thereafter, its sensitivity list determines when the association begins. The end block statement will then execute, said statement executes when a signal in its sensitivity list changes. For example, the statements associated with the sensitivity list @ clock will start executing when clock has an event. Bonus

Construct a decoder with five decoders with an enablebit.

Using a decoder and external gates, design the combinational circuit defined by the following three Boolean functions:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock