Question: $$Answer the Why highlighted below ; Answer No more than 3 lines and No Ai$$ Scheduling for Hyperthreading Platforms Federova's paper Assumptions Threads

$$Answer the "Why" highlighted below ; Answer No more than lines and No Ai$$ Scheduling for Hyperthreading Platforms

Federova's paper Assumptions

Threads issue instruction on each cycle CPU bound thread, a thread issues instructions that need to run on the CPU will be able to achieve a maximum metric in terms of instructions per cycle We cannot have an IPC greater than one 'instruction per cycle'

Memory access takes four cycles memorybound thread will experience some idle cycles while it's waiting for the memory access to return

Time takes to context switch among the different hardware threads is instantaneous no overheads into consideration

Let's also assume that we have a SMT with two hardware threads

Case Coschedule on Two Hardware Contexts

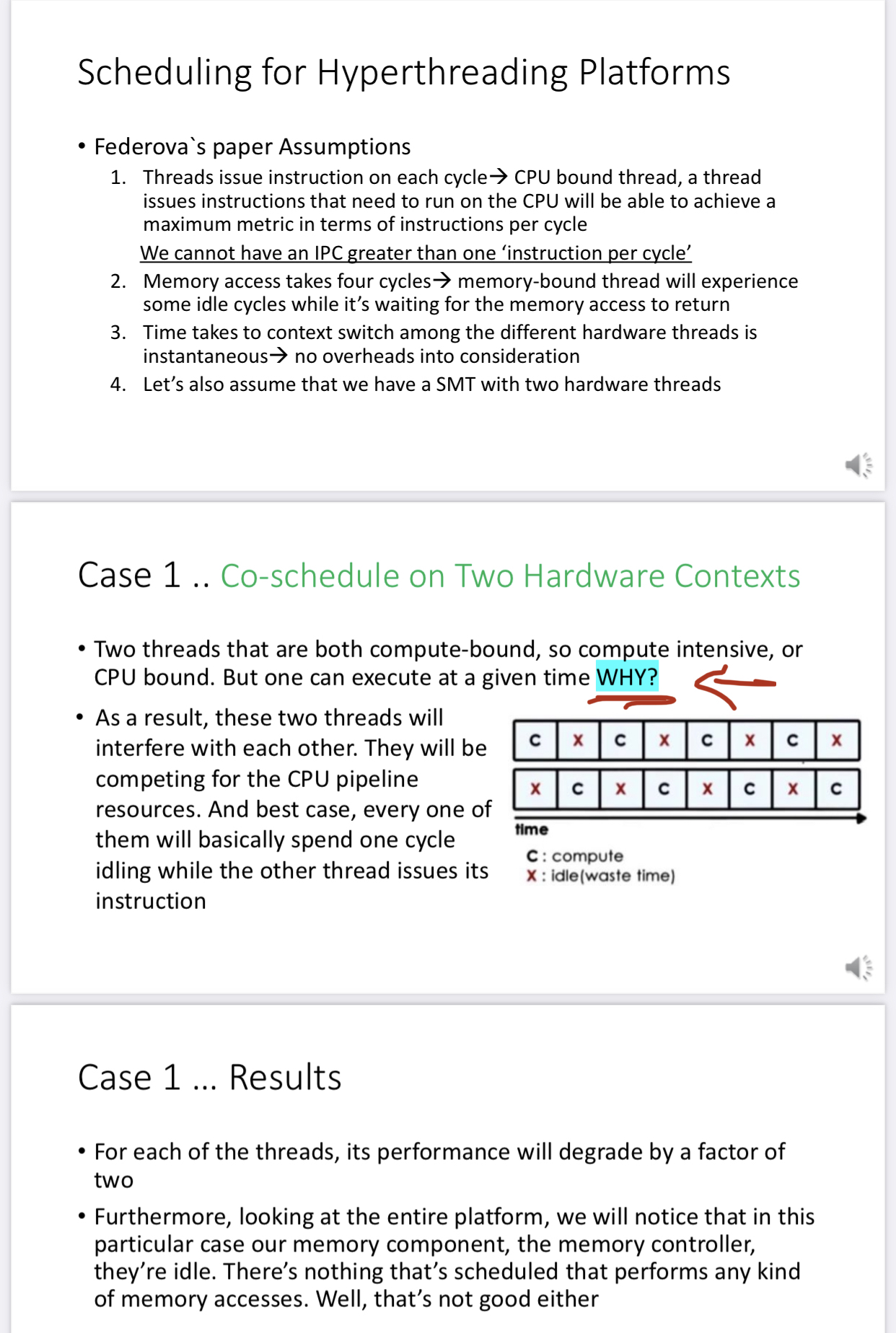

Two threads that are both computebound, so compute intensive, or CPU bound. But one can execute at a gir.

As a result, these two threads will interfere with each other. They will be competing for the CPU pipeline resources. And best case, every one of them will basically spend one cycle idling while the other thread issues its C: compute instruction

Case Results

For each of the threads, its performance will degrade by a factor of two

Furthermore, looking at the entire platform, we will notice that in this particular case our memory component, the memory controller, they're idle. There's nothing that's scheduled that performs any kind of memory accesses. Well, that's not good either

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock