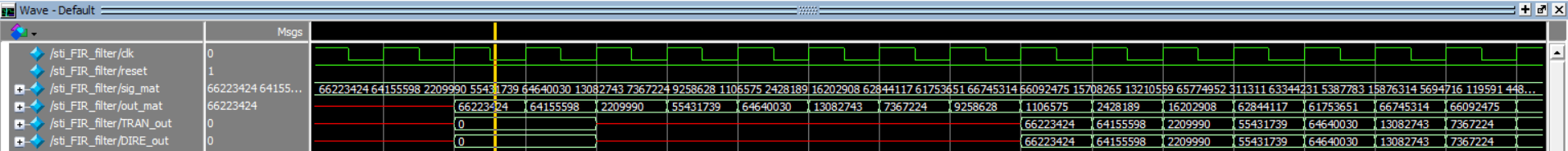

Question: As shown below, the two memory outputs ( TRAN _ out, DIRE _ out ) 0 are output for two clock cycles, and then the

As shown below, the two memory outputs TRANout, DIREout are output for two clock cycles, and then the x output is output for seven cycles before the desired output comes out. Please let me know we have to modify in the top module or in the stimulus file so that the desired output comes out immediatelywithout unlike i uploaded.outmat has to come out with TRANout and DIREout at the same time Assume that the modules instantiated in the top module are well defined.

module topFIRfilter input clk rstn

input signed : C C C C C C

;

wire signed : Xdirect, Xtranspose;

wire signed : Ydirect, Ytranspose;

reg NCEin NCEout;

wire NWRTin NWRTout;

reg : ADDRin ADDRout;

reg : statecount;

assign NWRTin b; read

assign NWRTout b; write

always @ posedge clk or negedge rstn

begin

ifrstn

begin

ADDRin b;

ADDRout b;

NCEin b;

NCEout b;

end

else

begin

ADDRin ADDRinb;

ADDRout ADDRoutb;

NCEin b;

NCEout b;

end

end

Memory for direct FIR filter

rflpxmx DIRECTINPUTMEM NWRTNWRTinDINRAADDRin:CAADDRin:NCENCEinCLKclkDOXdirect;

FIRfilterdirect DIRECTFIR clkclkrstnrstnXXdirectCCCCCCCCCCCCYYdirect;

rflpxmx DIRECTOUTPUTMEM NWRTNWRToutDINYdirectRAADDRout:CAADDRout:NCENCEoutCLKclkDO;

Memory for transpose FIR filter

rflpxmx TRANSINPUTMEM NWRTNWRTinDINRAADDRin:CAADDRin:NCENCEinCLKclkDOXtranspose;

FIRfiltertranspose TRANSFIR clkclkrstnrstnXXtransposeCCCCCCCCCCCCYYtranspose;

rflpxmx TRANSOUTPUTMEM NWRTNWRToutDINYtransposeRAADDRout:CAADDRout:NCENCEoutCLKclkDO;

endmodule

timescale nsps

module stiFIRfilter;

reg clk reset;

reg : sigmat :;

reg : outmat;

reg : TRANout;

reg : DIREout;

wire : chaa ;

wire : ch;

wire : che;

wire : cha;

wire : ch;

wire : chcd;

topFIRfilter FIRclk reset, c c c c c c;

integer err;

initial

begin

clk ;

reset ;

#

reset ;

end

always # clk ~clk;

initial $readmemhinputvectorhex.txt FIR.DIRECTINPUTMEM.array; check the path of memory rocation module instance

initial $readmemhinputvectorhex.txt FIR.TRANSINPUTMEM.array; check the path of memory rocation module instance

integer i;

initial

begin

$readmemhoutputvectorhex.txt sigmat;

#;

for i; i; ii

begin

outmat sigmati;

TRANout FIR.DIRECTOUTPUTMEM.arrayi;

DIREout FIR.TRANSOUTPUTMEM.arrayi;

ifTRANout outmatDIREout outmat err err ;

#;

end

$stop;

end

endmoduleL.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock