Question: As shown in class, one error detection technique is the addition of a parity bit to every transmitted word. Design a Mealy FSM ( using

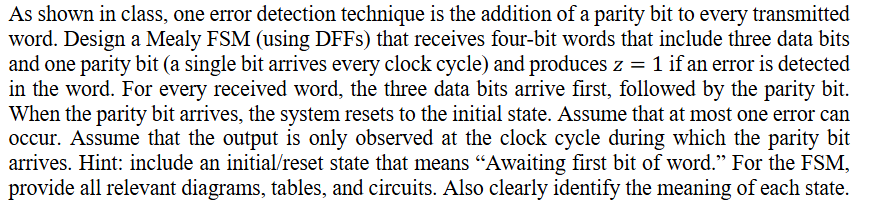

As shown in class, one error detection technique is the addition of a parity bit to every transmitted word. Design a Mealy FSM using DFFs that receives fourbit words that include three data bits and one parity bit a single bit arrives every clock cycle and produces z if an error is detected in the word. For every received word, the three data bits arrive first, followed by the parity bit. When the parity bit arrives, the system resets to the initial state. Assume that at most one error can occur. Assume that the output is only observed at the clock cycle during which the parity bit arrives. Hint: include an initialreset state that means "Awaiting first bit of word." For the FSM provide all relevant diagrams, tables, and circuits. Also clearly identify the meaning of each state.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock