Question: Assemble a memory system. Question 8: Assemble a memory system The schemati a microprocessor with a 32-bit wide data bus and a 24-bit wide address

Assemble a memory system.

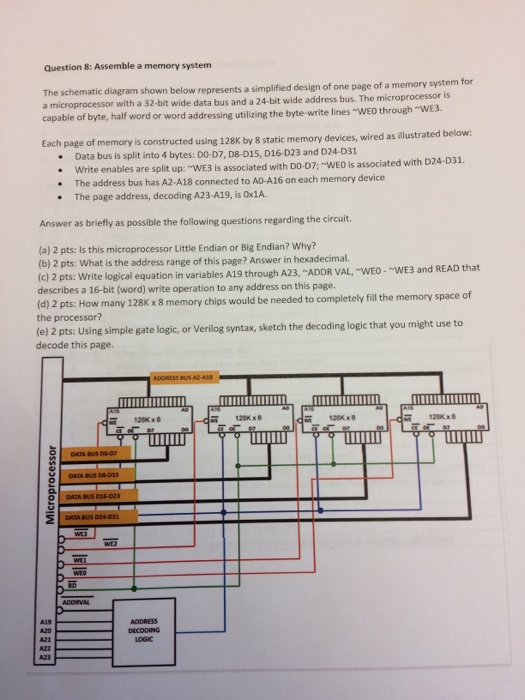

Question 8: Assemble a memory system The schemati a microprocessor with a 32-bit wide data bus and a 24-bit wide address bus. The microprocessor is C diagram shown below represents a simplified design of one page of a memory system for word or word addressing utilizing the byte-write lines WEO through "WE3. Each page of memory is constructed using 128K by 8 static memory devices, wired as illustrated below Data bus is split into 4 bytes: DO-D7, D8-D15, D16-D23 and D24-D31 Write enables are split up: "WE3 is associated with DO-D7: WEO is associated with D24-D31 .The address bus has A2-A18 connected to AO-A16 on each memory device The page address, decoding A23-A19, is Ox1A. Answer as briefly as possible the following questions regarding the circuit (a) 2 pts: Is this microprocessor Little Endian or Big Endian? Why? (b) 2 pts: What is the address range of this page? Answer in hexadecimal. 2 pts: Write logical equation in variables A19 through A23, "ADDR VAL, "WEO-WE3 and READ that describes a 16-bit (word) write operation to any address on this page. (d) 2 pts: How many the processor? (e) 2 pts: Using simple gate logic, or Verilog syntax, sketch the decoding logic that you might use to decode this page. 128K x 8 memory chips would be needed to completely fill the memory space of 126K x 128K x8 12Kx8 DATA BUS 00-07 DAIA BUS DE-D1S DAIABUS 024-031 ADDRESS

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts