Question: Assembly program was written using four types of instructions with latency and frequency as shown in the following table: a) Assume a single-issue not pipelined

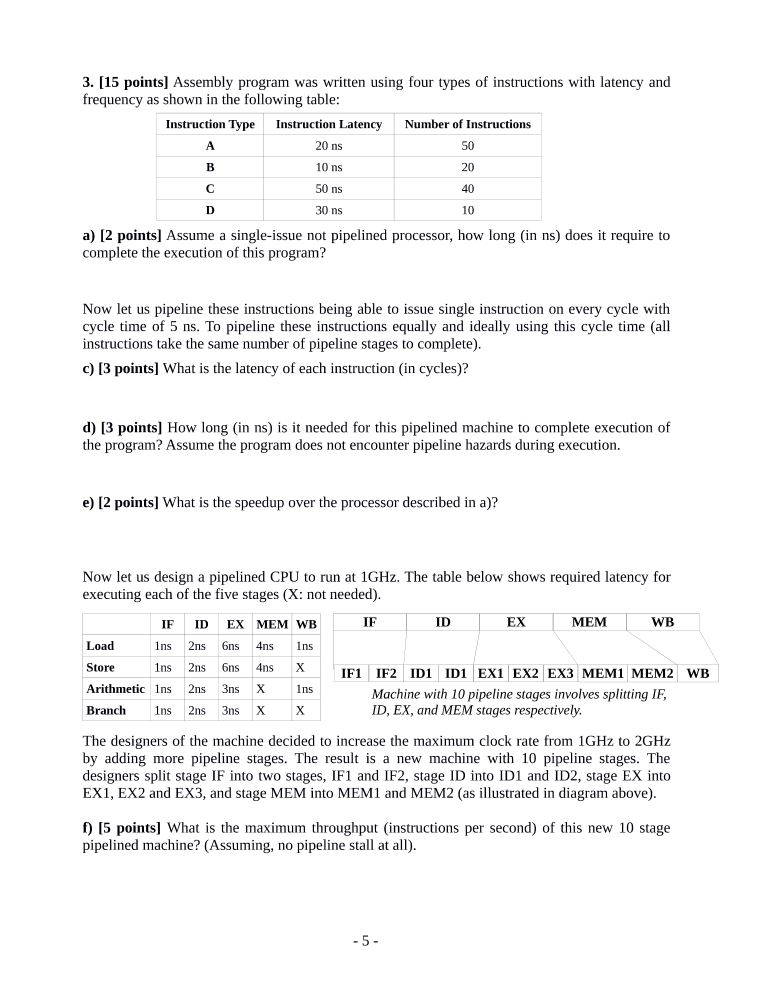

Assembly program was written using four types of instructions with latency and frequency as shown in the following table: a) Assume a single-issue not pipelined processor, how long (in ns) does it require to complete the execution of this program? Now let us pipeline these instructions being able to issue single instruction on every cycle with cycle time of 5 ns. To pipeline these instructions equally and ideally using this cycle time (all instructions take the same number of pipeline stages to complete). c) What is the latency of each instruction (in cycles)? d) How long (in ns) is it needed for this pipelined machine to complete execution of the program? Assume the program does not encounter pipeline hazards during execution. e) What is the speedup over the processor described in a)? Now let us design a pipelined CPU to run at 1GHz. The table below shows required latency for executing each of the five stages (X: not needed). The designers of the machine decided to increase the maximum clock rate from 1GHz to 2GHz by adding more pipeline stages. The result is a new machine with 10 pipeline stages. The designers split stage IF into two stages, IF1 and IF2, stage ID into ID1 and ID2, stage EX into EX1, EX2 and EX3, and stage MEM into MEM1 and MEM2 (as illustrated in diagram above). f) What is the maximum throughput (instructions per second) of this new 10 stage pipelined machine? (Assuming, no pipeline stall at all)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts