Question: Assignment: Modify the decoder in task 1 to show the sum (in decimals) of two 4-bit binary inputs. As only one decimal digit can be

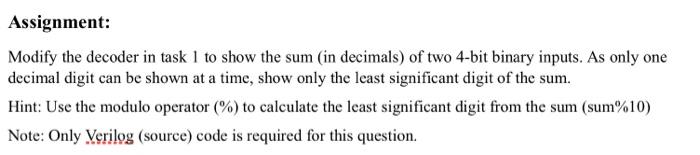

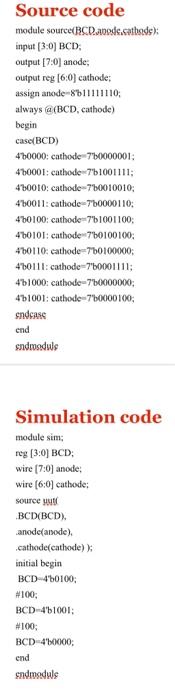

Assignment: Modify the decoder in task 1 to show the sum (in decimals) of two 4-bit binary inputs. As only one decimal digit can be shown at a time, show only the least significant digit of the sum. Hint: Use the modulo operator (\%) to calculate the least significant digit from the sum (sum\%10) Note: Only Verilog (source) code is required for this question. Source code module sourte(BCD.moode.5vthgds); input [3:0] BCD; output [7:0] anode; output reg [6:0] cathode; assign anode-8b11111110; always (a) (BCD, cathode) begin case(BCD) 4b0000: cathode 7 7b0000001: 4b0001: cathode 7b1001111: 4 b00t0: cathode 7 b0010010: 470011: cathode 770000110 ; 460100 : catbode=7b1001100; 4b0101: cathode 7 b0100100: 430110 : eathode 760100000 ; 4 b0111: cathode =7b00001111; 4b1000: cathode-7b0000000; 4b1001: cathode 7 bo000100: endcase end sndwosdubs Simulation code module sim: reg[3:0] BCD; wire [7:0] anode; wire [6;0] cathode; souree puty BCD(BCD), anode(anode), , cathode(cathode) ); initial begin BCD=460100; \#100; BCD 4 'b 100I; \#100; BCD4 'bo000; end sndmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts