Question: Assignment Objectives This assignment will help you practice working with bit vectors, bitwise operations, conditional logic, and behavioral modeling of combinational logic circuits in Verilog.

Assignment Objectives

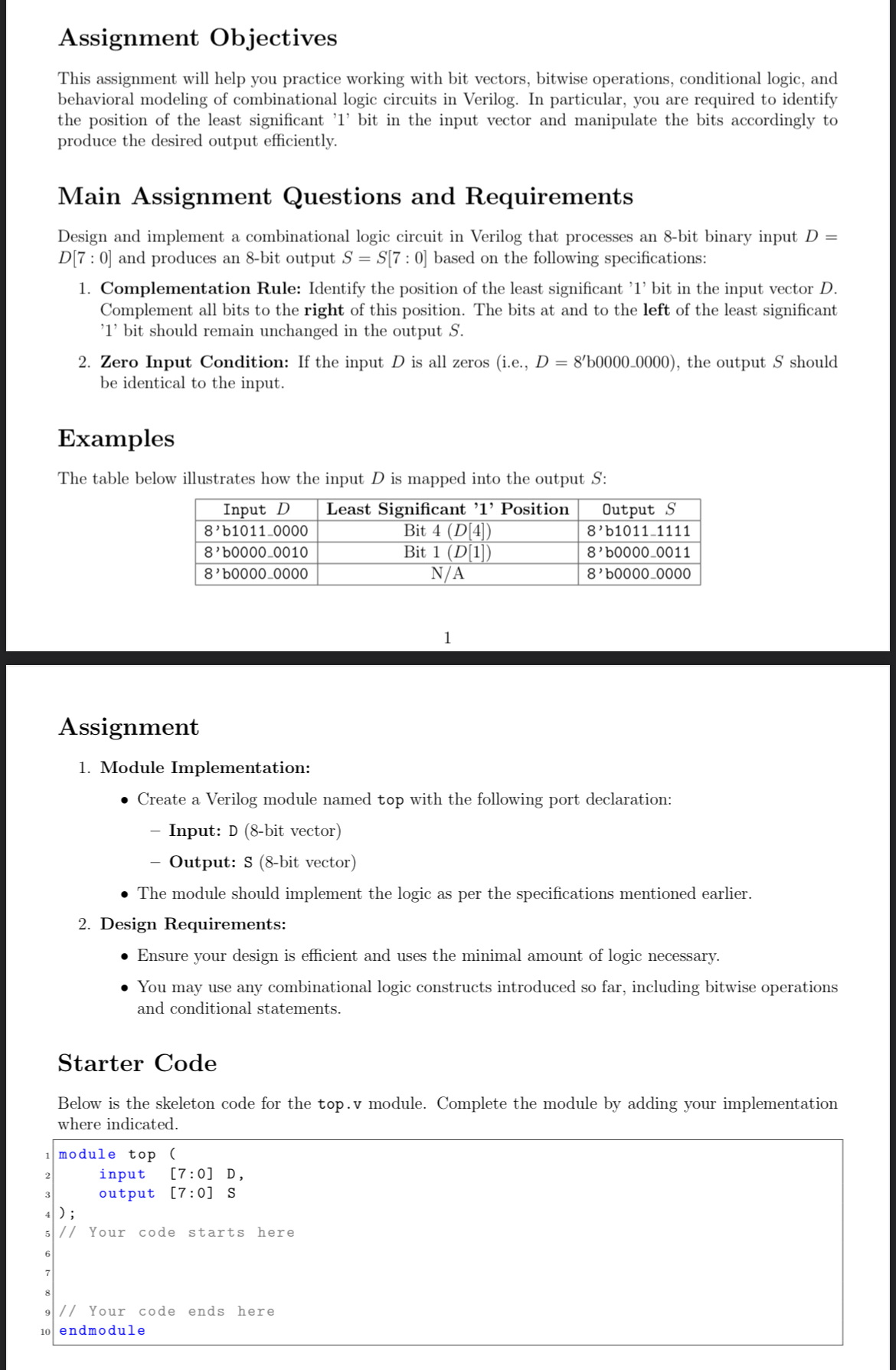

This assignment will help you practice working with bit vectors, bitwise operations, conditional logic, and behavioral modeling of combinational logic circuits in Verilog. In particular, you are required to identify the position of the least significant bit in the input vector and manipulate the bits accordingly to produce the desired output efficiently.

Main Assignment Questions and Requirements

Design and implement a combinational logic circuit in Verilog that processes an bit binary input : and produces an bit output : based on the following specifications:

Complementation Rule: Identify the position of the least significant bit in the input vector Complement all bits to the right of this position. The bits at and to the left of the least significant bit should remain unchanged in the output

Zero Input Condition: If the input is all zeros ie b the output should be identical to the input.

Examples

The table below illustrates how the input is mapped into the output :

tableInput Least Significant Position,Output SbBit DbbBit DbbNAb

Assignment

Module Implementation:

Create a Verilog module named top with the following port declaration:

Input: D bit vector

Output: S bit vector

The module should implement the logic as per the specifications mentioned earlier.

Design Requirements:

Ensure your design is efficient and uses the minimal amount of logic necessary.

You may use any combinational logic constructs introduced so far, including bitwise operations and conditional statements.

Starter Code

Below is the skeleton code for the top.v module. Complete the module by adding your implementation where indicated

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock