Question: Assume that your application has 400 data reads for each 6,000 instructions. For the same number of instruction the application has 200 data writes. The

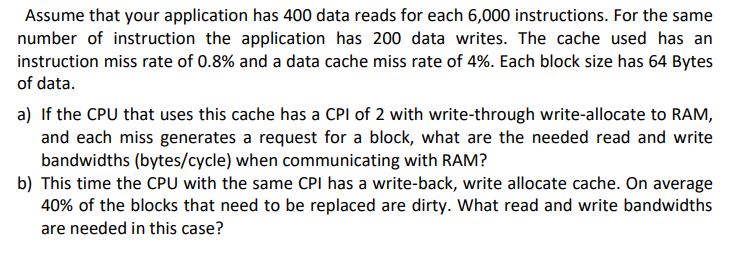

Assume that your application has 400 data reads for each 6,000 instructions. For the same number of instruction the application has 200 data writes. The cache used has an instruction miss rate of 0.8% and a data cache miss rate of 4%. Each block size has 64 Bytes of data a) If the CPU that uses this cache has a CPI of 2 with write-through write-allocate to RAM, and each miss generates a request for a block, what are the needed read and write bandwidths (bytes/cycle) when communicating with RAM? b) This time the CPU with the same CPI has a write-back, write allocate cache. On average 40% of the blocks that need to be replaced are dirty, what read and write bandwidths are needed in this case? Assume that your application has 400 data reads for each 6,000 instructions. For the same number of instruction the application has 200 data writes. The cache used has an instruction miss rate of 0.8% and a data cache miss rate of 4%. Each block size has 64 Bytes of data a) If the CPU that uses this cache has a CPI of 2 with write-through write-allocate to RAM, and each miss generates a request for a block, what are the needed read and write bandwidths (bytes/cycle) when communicating with RAM? b) This time the CPU with the same CPI has a write-back, write allocate cache. On average 40% of the blocks that need to be replaced are dirty, what read and write bandwidths are needed in this case

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts