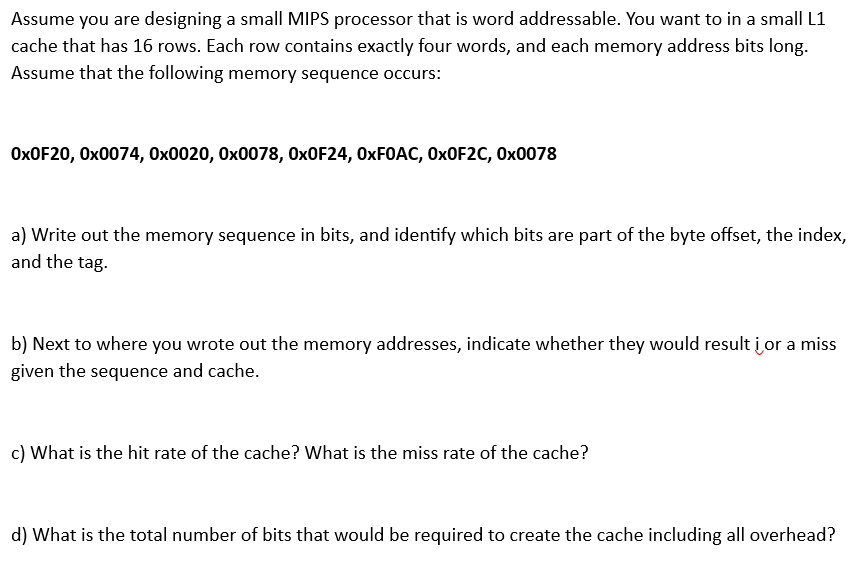

Question: Assume you are designing a small MIPS processor that is word addressable. You want to in a small L 1 cache that has 1 6

Assume you are designing a small MIPS processor that is word addressable. You want to in a small L

cache that has rows. Each row contains exactly four words, and each memory address bits long.

Assume that the following memory sequence occurs:

xFxxxxFxFOAC, xFCx

a Write out the memory sequence in bits, and identify which bits are part of the byte offset, the index,

and the tag.

b Next to where you wrote out the memory addresses, indicate whether they would result i or a miss

given the sequence and cache.

c What is the hit rate of the cache? What is the miss rate of the cache?

d What is the total number of bits that would be required to create the cache including all overhead?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock