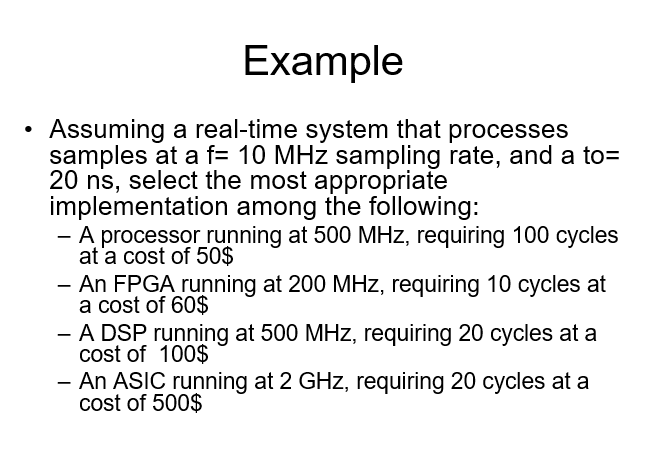

Question: - Assuming a real-time system that processes samples at a f=10MHz sampling rate, and a to= 20 ns, select the most appropriate implementation among the

- Assuming a real-time system that processes samples at a f=10MHz sampling rate, and a to= 20 ns, select the most appropriate implementation among the following: - A processor running at 500MHz, requiring 100 cycles at a cost of 50$ - An FPGA running at 200MHz, requiring 10 cycles at a cost of 60$ - A DSP running at 500MHz, requiring 20 cycles at a cost of 100$ - An ASIC running at 2GHz, requiring 20 cycles at a cost of 500$

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts