Question: (b) Write a SystemVerilog model of the state machine shown in Figure 1, with one procedural block for the state variable register and one procedural

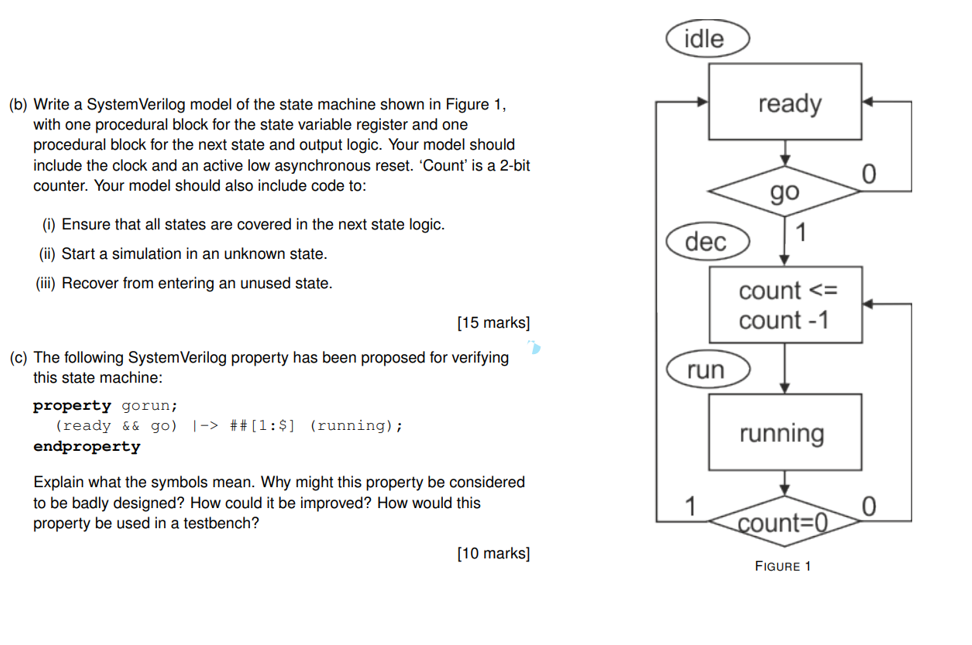

(b) Write a SystemVerilog model of the state machine shown in Figure 1, with one procedural block for the state variable register and one procedural block for the next state and output logic. Your model should include the clock and an active low asynchronous reset. 'Count' is a 2-bit counter. Your model should also include code to: (i) Ensure that all states are covered in the next state logic. (ii) Start a simulation in an unknown state. (iii) Recover from entering an unused state. [15 marks] (c) The following SystemVerilog property has been proposed for verifying this state machine: property gorun; (ready \&\& go) \#\#\#[1:\$] (running); endproperty Explain what the symbols mean. Why might this property be considered to be badly designed? How could it be improved? How would this property be used in a testbench

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts