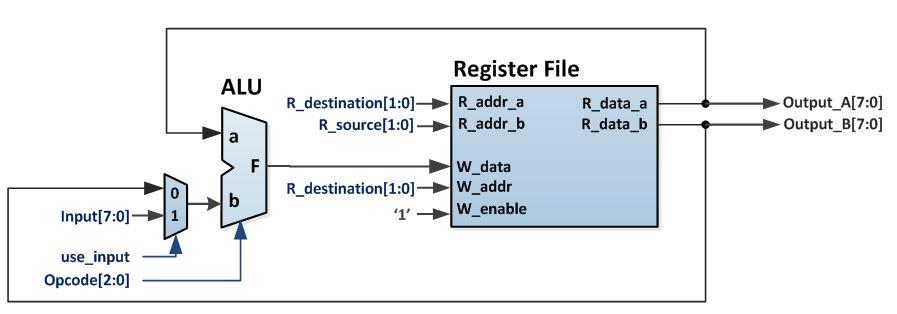

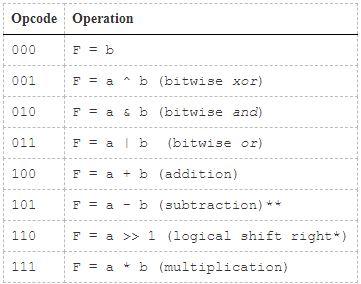

Question: Based on the following schematic and table please complete the second table below. Descriptions can be short and straight to the point. ALU Register File

Based on the following schematic and table please complete the second table below. Descriptions can be short and straight to the point.

![File R_destination(1:0) - R_addr_a R_data_a R_source(1:0) - R_addr_b R_data_b Output_A[7:0] Output_B[7:0] a](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f3e609a02f4_16966f3e60940e2d.jpg)

ALU Register File R_destination(1:0) - R_addr_a R_data_a R_source(1:0) - R_addr_b R_data_b Output_A[7:0] Output_B[7:0] a F 0 1 W_data W_addr W_enable R_destination(1:0) - '1' b Input[7:0) use_input Opcode(2:0) Opcode Operation 000 F = b 001 F = a b (bitwise xor) 010 F =a & b (bitwise and) 011 F = a b (bitwise or) 100 F = a + b (addition) 101 F = a - b (subtraction) ) 110 F = a >> 1 (logical shift right*) 111 F = a + b (multiplication) Machine Code Register Operation Description Opcode use_input 0 Rd

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts