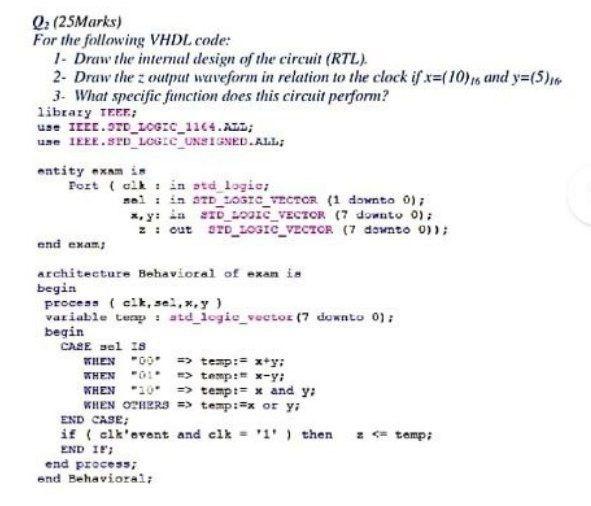

Question: : C. (25Marks) For the following VHDL code: 1- Draw the internal design of the circuit (RTL). 2- Draw the z output waveform in relation

: C. (25Marks) For the following VHDL code: 1- Draw the internal design of the circuit (RTL). 2- Draw the z output waveform in relation to the clock if.x=(10) and y=(5) 3- What specific function does this circuit perform? library TEET: use IEEE.9TD_LOGZC_1164.AD; use IEEE. SID_LOGIC_UNSIGNED. ALL entity exam is Pezt ( ok : in atd logie; -1 in STD_3067C_TECTOR (1 downto 0); *, y: 210_2091C_VECTOR (7 domuto 0); 2 : cut STD_LOGIC_VECTOR (7 downto 0)); end exams architecture Behavioral of exan i. begin process (cik, sel, m.) variable tem : atd_logie_veetoz (7 downto 0); begin CASE sel zs -00 => temp:= x+y: WHEN #> temp: x-y: WHEN "20- => temp = x and y: WHEN OTHERS => temp:*or y END CASE; if ( elk'eront and clk = '1') then 24 tempi END IF end process; and Behavioral: WHEN : C. (25Marks) For the following VHDL code: 1- Draw the internal design of the circuit (RTL). 2- Draw the z output waveform in relation to the clock if.x=(10) and y=(5) 3- What specific function does this circuit perform? library TEET: use IEEE.9TD_LOGZC_1164.AD; use IEEE. SID_LOGIC_UNSIGNED. ALL entity exam is Pezt ( ok : in atd logie; -1 in STD_3067C_TECTOR (1 downto 0); *, y: 210_2091C_VECTOR (7 domuto 0); 2 : cut STD_LOGIC_VECTOR (7 downto 0)); end exams architecture Behavioral of exan i. begin process (cik, sel, m.) variable tem : atd_logie_veetoz (7 downto 0); begin CASE sel zs -00 => temp:= x+y: WHEN #> temp: x-y: WHEN "20- => temp = x and y: WHEN OTHERS => temp:*or y END CASE; if ( elk'eront and clk = '1') then 24 tempi END IF end process; and Behavioral: WHEN

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts