Question: Cache Coherence ( 4 0 pts ) 3 . Consider the following reference stream: r 2 ( A ) , w 2 ( B )

Cache Coherence pts

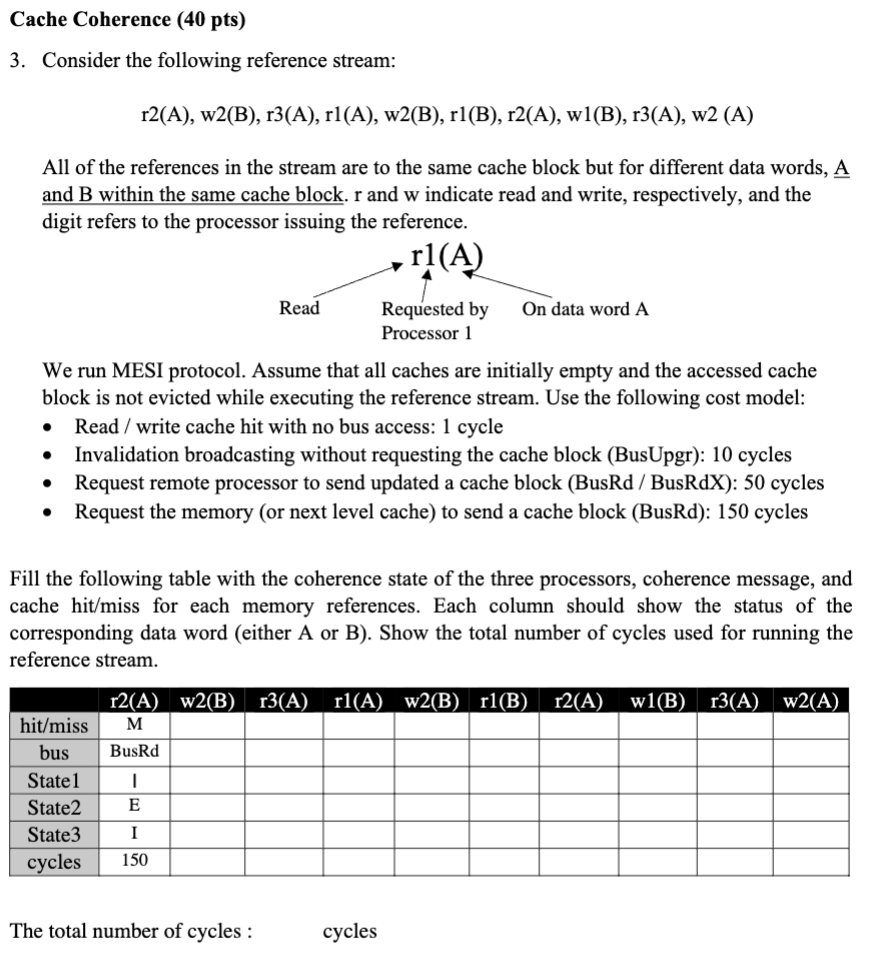

Consider the following reference stream:

rA wB rA rA wB rB rA wB rA wA

All of the references in the stream are to the same cache block but for different data words, A

and B within the same cache block. r and w indicate read and write, respectively, and the

digit refers to the processor issuing the reference.

rA

We run MESI protocol. Assume that all caches are initially empty and the accessed cache

block is not evicted while executing the reference stream. Use the following cost model:

Read write cache hit with no bus access: cycle

Invalidation broadcasting without requesting the cache block BusUpgr: cycles

Request remote processor to send updated a cache block BusRd BusRdX: cycles

Request the memory or next level cache to send a cache block BusRd: cycles

Fill the following table with the coherence state of the three processors, coherence message, and

cache hitmiss for each memory references. Each column should show the status of the

corresponding data word either A or B Show the total number of cycles used for running the

reference stream

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock