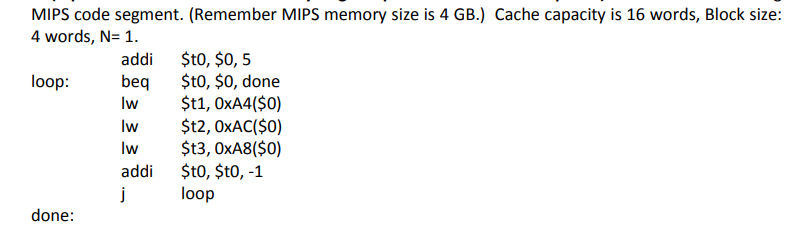

Question: Cache Memory MIPS code segment. (Remember MIPS memory size is 4 GB.) Cache capacity is 16 words, Block size: 4 words, N=1. addi $to, $0,5

Cache Memory

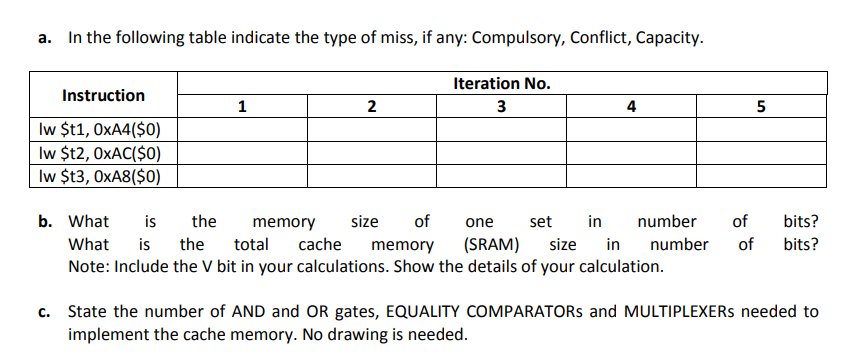

MIPS code segment. (Remember MIPS memory size is 4 GB.) Cache capacity is 16 words, Block size: 4 words, N=1. addi $to, $0,5 loop: beq $t0,$0, done Iw $t1, OxA4($0) Iw $t2, OxAC($0) lw $t3, 0xA8($0) addi $t0,$t0, -1 j loop done: a. In the following table indicate the type of miss, if any: Compulsory, Conflict, Capacity. Instruction Iteration No. 3 1 2 4 5 lw $t1, OxA4($0) lw $t2, OxAC($0) lw $t3, OxA8($0) one b. What is the memory size of set in number What is the total cache memory (SRAM) size in number Note: Include the V bit in your calculations. Show the details of your calculation. of of bits? bits? C. State the number of AND and OR gates, EQUALITY COMPARATORS and MULTIPLEXERs needed to implement the cache memory. No drawing is needed

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts