Question: Can you help me solve the coding problems for this homework. If test bench code is needed I can provide. ( The remaining parameters, w

Can you help me solve the coding problems for this homework. If test bench code is needed I can provide.

The remaining parameters, wfp and wfp are set to the full size of the two

FP formats used, don't change them. Inputs a and b format

with a wexpbit exponent and a wsigbit significand. The total size of each of these inputs is

expwsig bits. The custom format is recognized by the Chipware modules. The value on

input c is a wcbit unsigned integer. The value on output ssum is expected to be a IEEEformat

FP number with a wexpbit exponent and wsigbit significand.

The output ssum scaled sum is to be set to and output gt is to be set to if

and otherwise.

For this problem one should review the IEEE notes, plus the use of the Verilog concate

nation like shift and bit slice : operators.

a Modify compfp so that it computes without using Chipware modules. The value does not

have to be assigned to any particular object, but it should be used to compute To solve

this subproblem one must understand the IEEE format. A correct solution requires just a line

or two of Verilog code. Just one line if overflow is ignored, which is okay.

Compute without Chipware modules.

b Modify compfp so that ssum is set to For partial credit, or to get started quickly

set ssum to If this is done correctly the testbench tests should show zero ss errors.

Compute the sum using Chipware modules and the value of from the previous part.

Note that a and b have a wsigbit significand, but the sum should have a wsigbit signif

icand. So the significands of and must be lengthened assume that wsig wsig See

the description of the IEEE format. Please don't look for a module to do this for you.

Convert and into FP types with a wsigbit significand.

Using the value from the previous part, set ssum to

c Modify compfp so that gt is correctly set using a floatingpoint comparison. Don't forget that

input c carries an unsigned integer so that to do a FP comparison c will need to be converted.

Set gt

Use Chipware modules for floatingpoint computation and floatingpointinteger conversion.

Use procedural or implicit structural assign code for any integer computation.

Pay attention to cost: don't use more bits than are needed.

The modules must be synthesizable.

Problem : Module compint has the same connections as compfp and its outputs should be

set to the same values.

a Modify compint so that it computes ssum using an instantiation of compfp The ssum output

the compfp instance should connect to the ssum output of compint. Don't use the gt output

of compfp so that the synthesis program doesn't synthesize compfp hardware for gt

Compute ssum using an instance of compfp asbc where inputs a and are

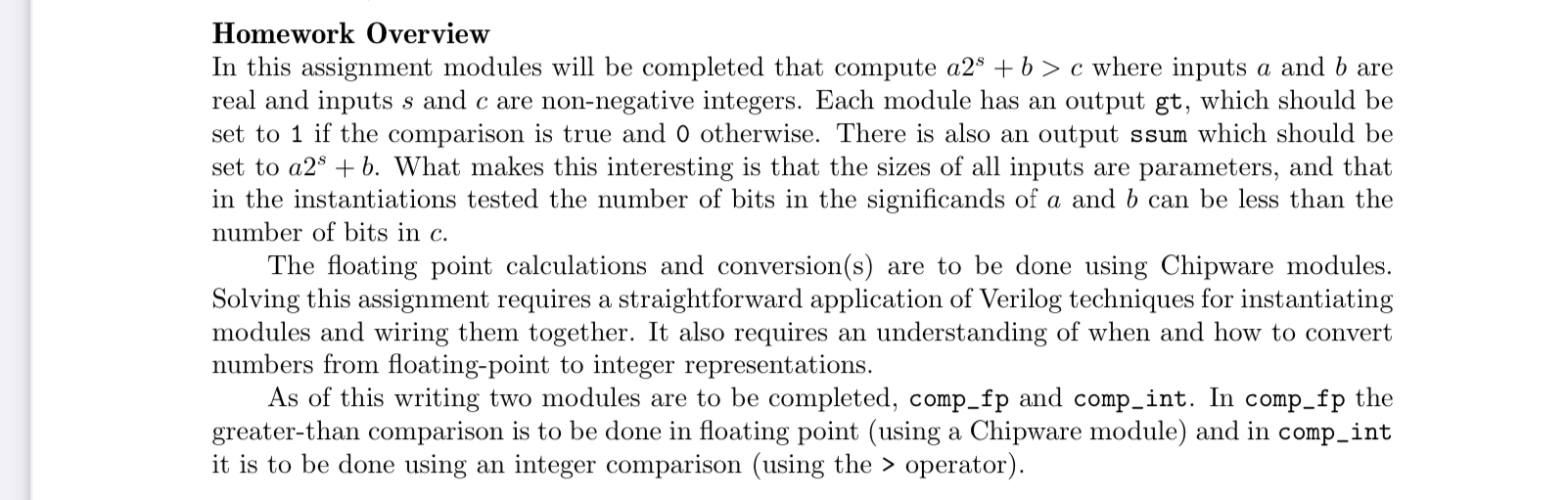

real and inputs and are nonnegative integers. Each module has an output gt which should be

set to if the comparison is true and otherwise. There is also an output ssum which should be

set to What makes this interesting is that the sizes of all inputs are parameters, and that

in the instantiations tested the number of bits in the significands of a and can be less than the

number of bits in

The floating point calculations and conversions are to be done using Chipware modules.

Solving this assignment requires a straightforward application of Verilog techniques for instantiating

wirithem tIt also requires an understanding of when and how to convert

two modules are to be completed, compfp and coe

greaterthan comparison is to be done in floating point using a Chipware module and in comp using an integer c Compute gt using an integer co

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock