Question: can you please help me ( Q7) (in C programming language and Unix systems lab) 04- Lets consider a virtual address translation using a two-level

can you please help me ( Q7) (in C programming language and Unix systems lab)

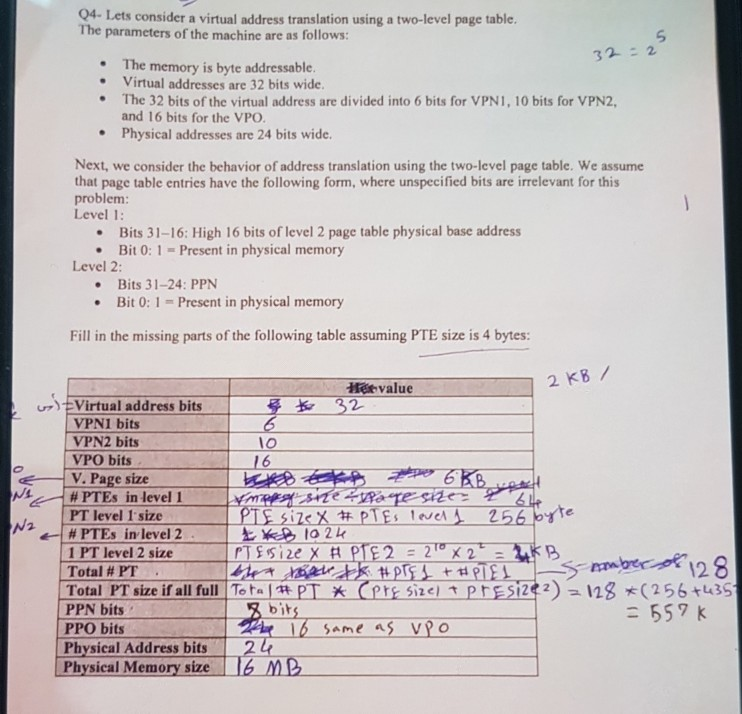

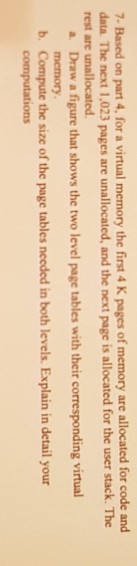

04- Lets consider a virtual address translation using a two-level page table. he parameters of the machine are as follows: 32 2 The memory is byte addressable Virtual addresses are 32 bits wide The 32 bits of the virtual address are divided into 6 bits for VPN1, 10 bits for VPN2, and 16 bits for the VPO Physical addresses are 24 bits wide. Next, we consider the behavior of address translation using the two-level page table. We assume that page table entries have the following form, where unspecified bits are irrelevant for this problem Level 1: Bits 31-16: High 16 bits of level 2 page table physical base address Bit 0: 1 Present in physical memory Level 2: Bits 31-24: PPN Bit 0:1 Present in physical memory Fill in the missing parts of the following table assuming PTE size is 4 bytes: Heevalue ur)Virtual address bits 32 VPNI bits 6 VPN2 bits VPO bits EV.Page size # PTEs in level i PT level 1 size d # PTEs ir level 2 | t. 1 PT level 2 size PIS size X H PIE22T 2B Total # PT Total PT size if all full | Tetlit PT Cork size, t p r ES'n 2) PPN bits PPO bits Physical Address bits 2 Physical Memory size6 MR mn +- 128(2 5 6435 bih 557K 16 same aS V O 7- Based on part 4, for a virtual memory the first 4 K pages of memory are allocated for code and data. The next 1,023 pages are unallocated, and the next page is allocated for the user stack. The rest are unallocated Draw a figure that shows the two level page tables with their corresponding virtual memory Compute the size of the page tables needed in both levels. Explain in detail your computations a. b. 04- Lets consider a virtual address translation using a two-level page table. he parameters of the machine are as follows: 32 2 The memory is byte addressable Virtual addresses are 32 bits wide The 32 bits of the virtual address are divided into 6 bits for VPN1, 10 bits for VPN2, and 16 bits for the VPO Physical addresses are 24 bits wide. Next, we consider the behavior of address translation using the two-level page table. We assume that page table entries have the following form, where unspecified bits are irrelevant for this problem Level 1: Bits 31-16: High 16 bits of level 2 page table physical base address Bit 0: 1 Present in physical memory Level 2: Bits 31-24: PPN Bit 0:1 Present in physical memory Fill in the missing parts of the following table assuming PTE size is 4 bytes: Heevalue ur)Virtual address bits 32 VPNI bits 6 VPN2 bits VPO bits EV.Page size # PTEs in level i PT level 1 size d # PTEs ir level 2 | t. 1 PT level 2 size PIS size X H PIE22T 2B Total # PT Total PT size if all full | Tetlit PT Cork size, t p r ES'n 2) PPN bits PPO bits Physical Address bits 2 Physical Memory size6 MR mn +- 128(2 5 6435 bih 557K 16 same aS V O 7- Based on part 4, for a virtual memory the first 4 K pages of memory are allocated for code and data. The next 1,023 pages are unallocated, and the next page is allocated for the user stack. The rest are unallocated Draw a figure that shows the two level page tables with their corresponding virtual memory Compute the size of the page tables needed in both levels. Explain in detail your computations a. b

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts