Question: CIS 273: Computer Organization & Design Homework #5-The Final Homework Electronic submissions to mycourses, on or before the due date. 1. (30 points) For each

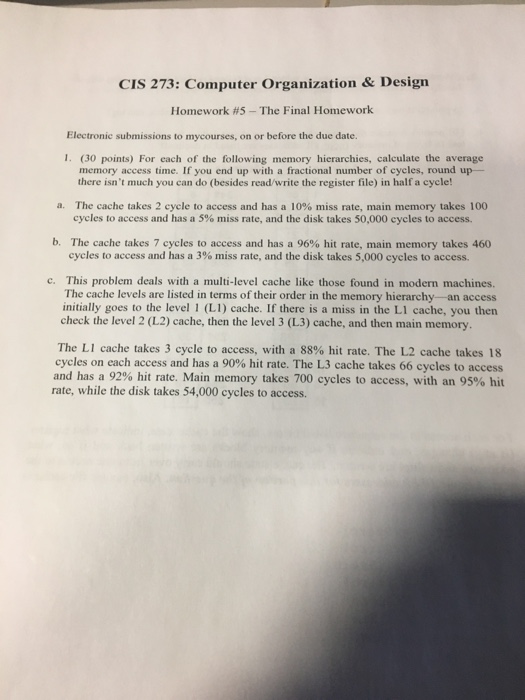

CIS 273: Computer Organization & Design Homework #5-The Final Homework Electronic submissions to mycourses, on or before the due date. 1. (30 points) For each of the following memory hierarchies, calculate the average memory access time. If you end up with a fractional number of cycles, round up- there isn't much you can do (besides read/write the register file) in half a cycle! cycles to access and has a 5% miss rate, and the disk takes 50,000 cycles to access. cycles to access and has a 3% miss rate, and the disk takes 5,000 cycles to access. a. The cache takes 2 cycle to access and has a 10% miss rate, main memory takes 100 b, The cache takes 7 cycles to access and has a 96% hit rate, main memory takes 460 This problem deals with a multi-level cache like those found in modern machines. The cache levels are listed in terms of their order in the memory hierarchy-an access initially goes to the level 1 (L1) cache. If there is a miss in the L1 cache, you then c. check the level 2 (L2) cache, then the level 3 (L3) cache, and then main memory. The L1 cache takes 3 cycle to access, with a 88% hit rate. The L2 cache takes 18 cycles on each access and has a 90% hit rate. The L3 cache takes 66 cycles to access and has a 92% hit rate. Main memory takes 700 cycles to access, with an 95% hit rate, while the disk takes 54,000 cycles to access

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts