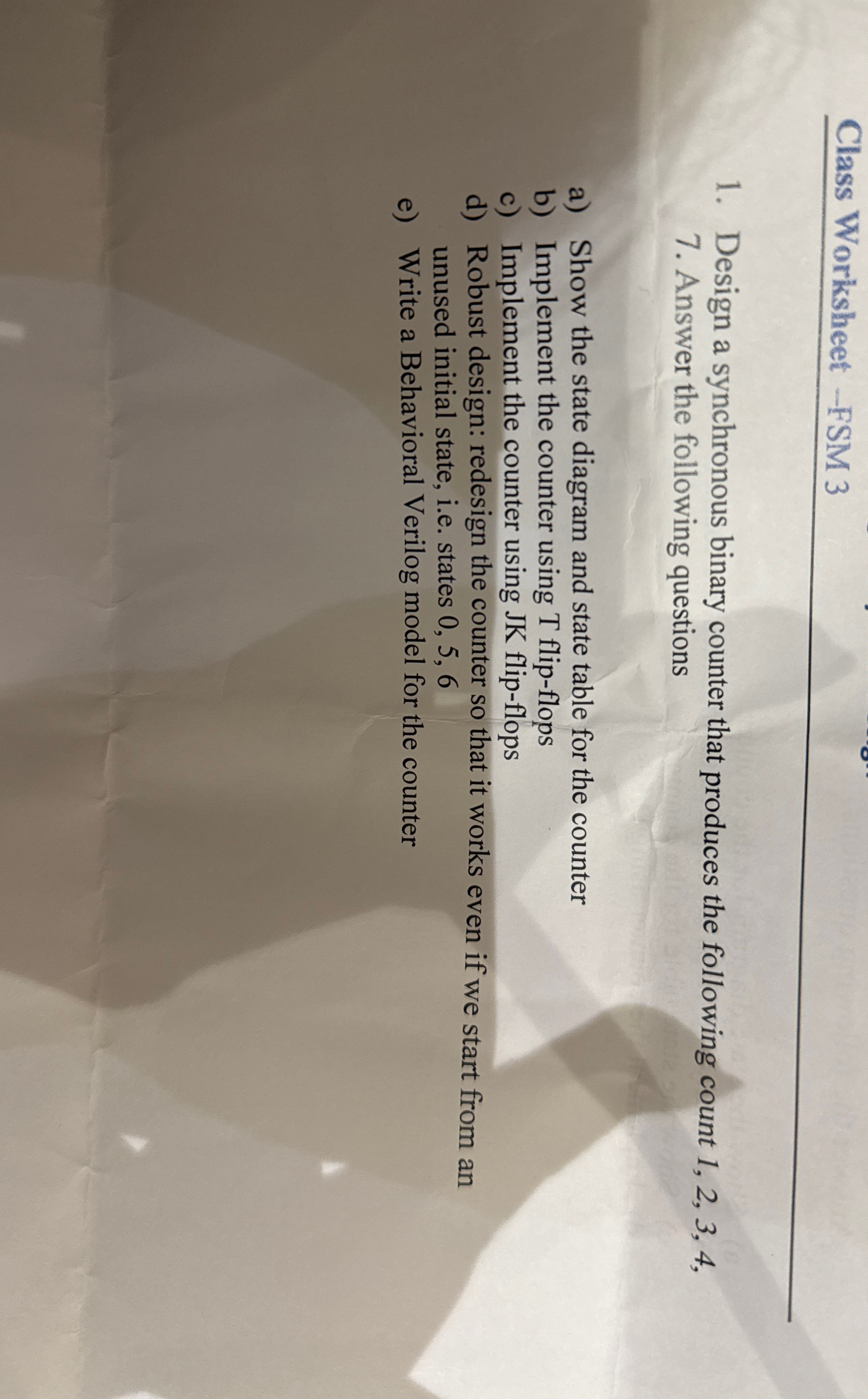

Question: Class Worksheet - FSM 3 Design a synchronous binary counter that produces the following count 1 , 2 , 3 , 4 , 7 .

Class Worksheet FSM

Design a synchronous binary counter that produces the following count Answer the following questions

a Show the state diagram and state table for the counter

b Implement the counter using T flipflops

c Implement the counter using JK flipflops

d Robust design: redesign the counter so that it works even if we start from an unused initial state, ie states

e Write a Behavioral Verilog model for the counter

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock