Question: + COA - RT - Lesson 10- Cache MX -RT - Lesson 08 - 2SP pdf ECOART - Lesson 09 - 2Sp.pdf Nat syncit G

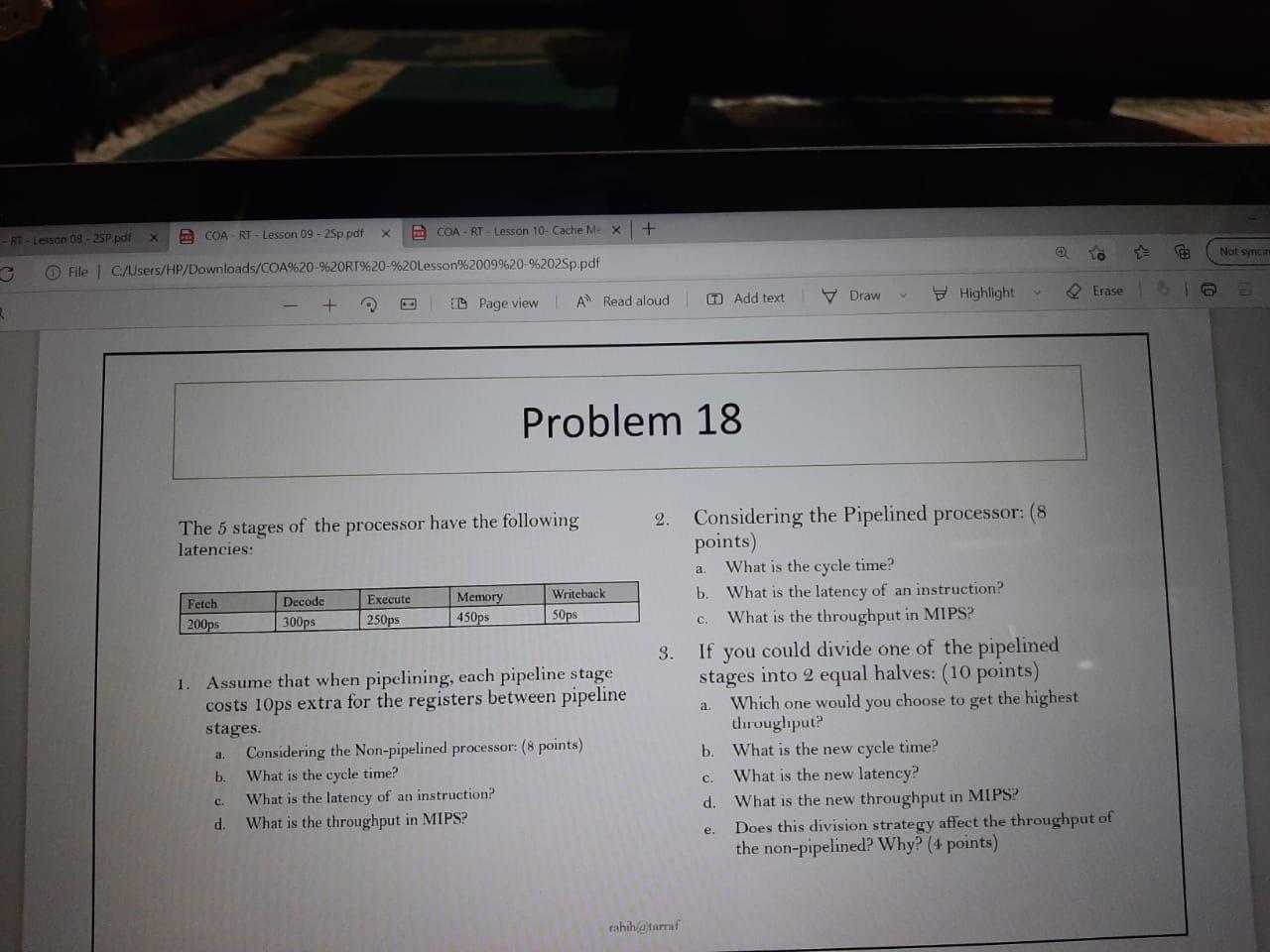

+ COA - RT - Lesson 10- Cache MX -RT - Lesson 08 - 2SP pdf ECOART - Lesson 09 - 2Sp.pdf Nat syncit G File C/Users/HP/Downloads/COA%20-%20RT%20-%20Lesson%2009%20-%202Sp.pdf ID Page view A Read aloud Erase 0 Add text Draw Highlight 2 Problem 18 The 5 stages of the processor have the following latencies: a. Fetch 200ps Decode 300ps Execute 250ps Memory 450ps Writeback 50ps c. 2. Considering the Pipelined processor: (8 points) What is the cycle time? b. What is the latency of an instruction? What is the throughput in MIPS? S. If you could divide one of the pipelined stages into 2 equal halves: (10 points) Which one would you choose to get the highest throughput? b. What is the new cycle time? What is the new latency? What is the new throughput in MIPS? Does this division strategy affect the throughput of the non-pipelined? Why? (4 points) 1. Assume that when pipelining, each pipeline stage costs 10ps extra for the registers between pipeline stages. Considering the Non-pipelined processor: (8 points) What is the cycle time? What is the latency of an instruction? What is the throughput in MIPS? a b C. C. d. d. e. mahihi @ karena

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts