Question: Complex FSM Design ( run detector ) For this assignment you will design a FSM that will control several registers to count runs of length

Complex FSM Design run detector

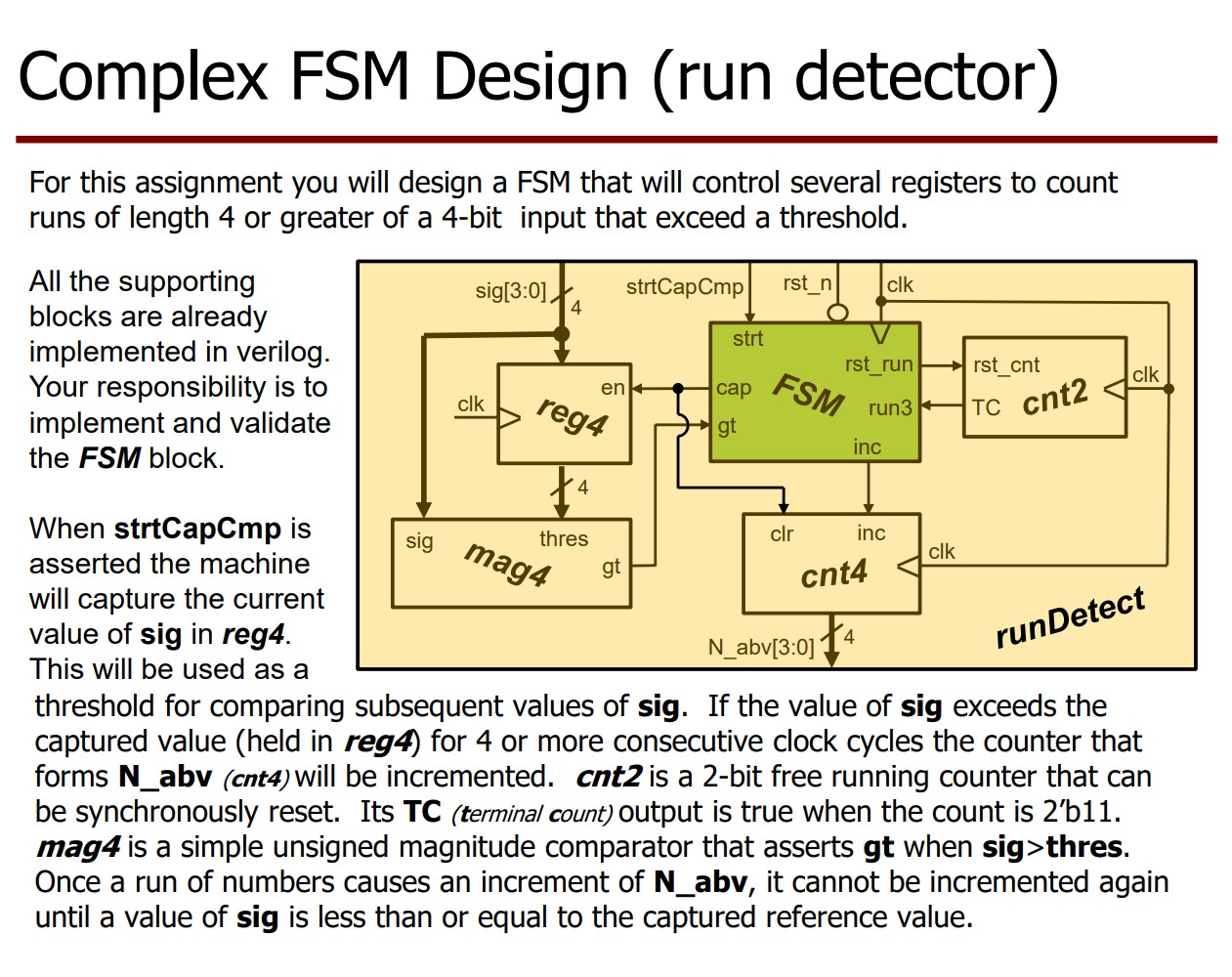

For this assignment you will design a FSM that will control several registers to count

runs of length or greater of a bit input that exceed a threshold.

All the supporting

blocks are already

implemented in verilog.

Your responsibility is to

implement and validate

the FSM block.

When strtCapCmp is

asserted the machine

will capture the current

value of sig in reg

This will be used as a

threshold for comparing subsequent values of sig. If the value of sig exceeds the

captured value held in reg for or more consecutive clock cycles the counter that

forms Nabv cnt will be incremented. cht is a bit free running counter that can

be synchronously reset. Its TC terminal count output is true when the count is b

mag is a simple unsigned magnitude comparator that asserts gt when sigthres.

Once a run of numbers causes an increment of Nabv, it cannot be incremented again

until a value of sig is less than or equal to the captured reference value. Please draw out the FSM

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock