Question: Compute a C++ code of this procedure I A 4-stage pipelined CPU architecture is shown below with Fetch, Decode, Execute and Store stages. The Instructions

Compute a C++ code of this procedure

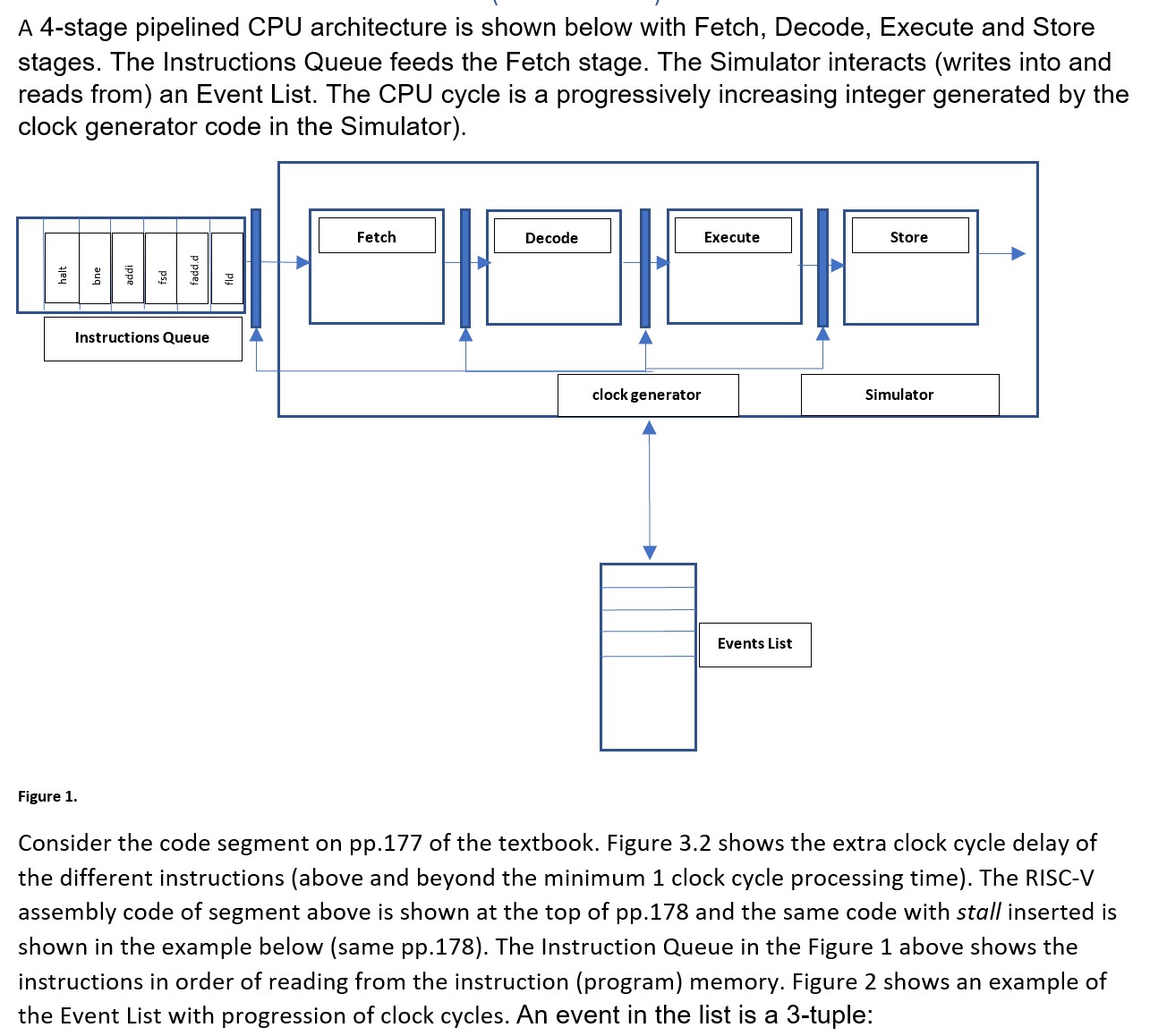

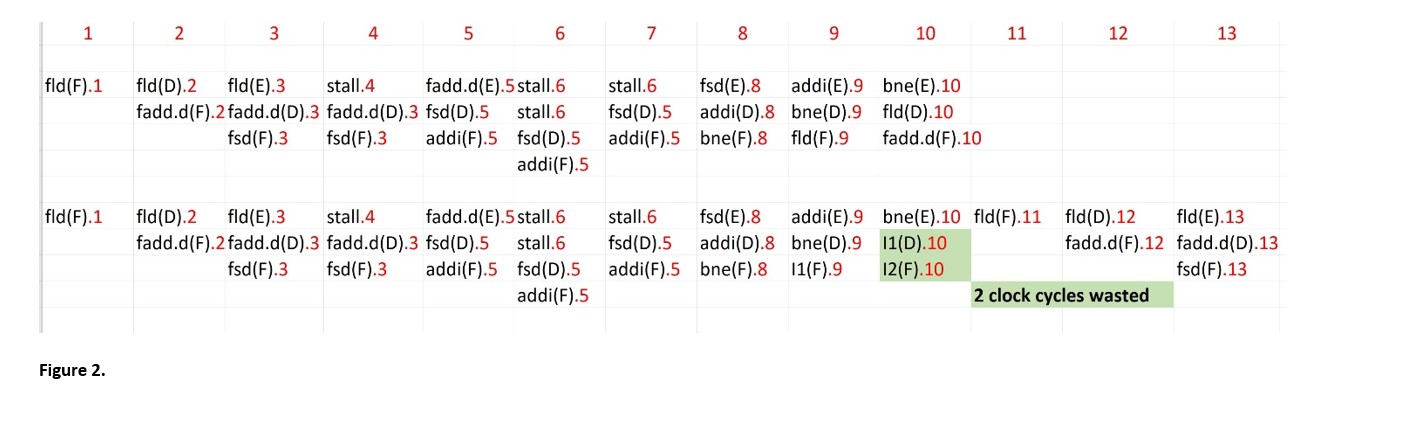

I A 4-stage pipelined CPU architecture is shown below with Fetch, Decode, Execute and Store stages. The Instructions Queue feeds the Fetch stage. The Simuiator interacts (writes into and reads from) an Event List. The CPU cycle is a progressively increasing integer generated by the ciock generator code in the Simulator). Fetch Decode Execute Store halt brie add i 511 fadd .d fld Instructions Queue clock generator Simulator Events List Figure 1. Consider the code segment on pp.177 of the textbook. Figure 3.2 shows the extra clock cycle delay of the different instructions (above and beyond the minimum 1 clock cycle processing time). The RISCV assembly code of segment above is shown at the top of pp.178 and the same code with stall inserted is shown in the exampie below (same pp.178). The instruction Queue in the Figure 1 above shows the instructions in order of reading from the instruction (program) memory. Figure 2 shows an example of the Event List with progression of ciock cycles. An event in the list is a 3-tuple: \f

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts