Question: Computer Architecture and System Design (a) (b) 2. (a) Work out the multi-level carry lookahead scheme for doing a 32-bit number addition by 2 methods.

Computer Architecture and System Design

(a)

(b)

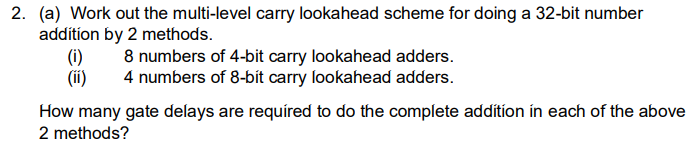

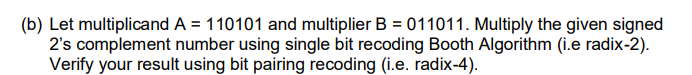

2. (a) Work out the multi-level carry lookahead scheme for doing a 32-bit number addition by 2 methods. (i) 8 numbers of 4-bit carry lookahead adders. (ii) 4 numbers of 8-bit carry lookahead adders. How many gate delays are required to do the complete addition in each of the above 2 methods? (b) Let multiplicand A = 110101 and multiplier B = 011011. Multiply the given signed 2's complement number using single bit recoding Booth Algorithm (i.e radix-2). Verify your result using bit pairing recoding (i.e. radix-4)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts