Question: Computer architecture question. For a dual-issue superscalar processor with two integer units and one load/store unit, diagram how each instruction moves through the pipeline. Indicate

Computer architecture question.

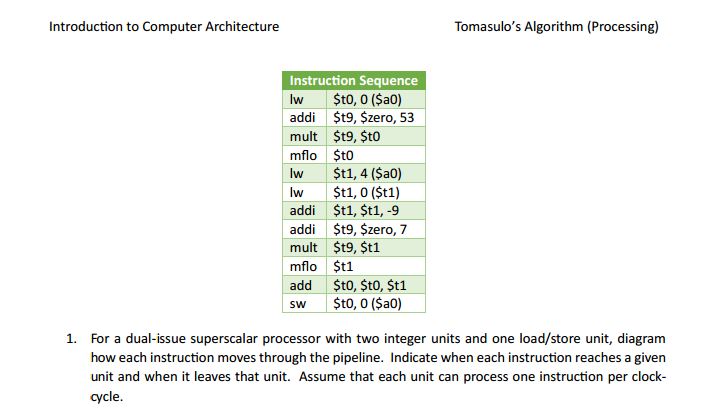

For a dual-issue superscalar processor with two integer units and one load/store unit, diagram how each instruction moves through the pipeline. Indicate when each instruction reaches a given unit and when it leaves that unit. Assume that each unit can process one instruction per clockcycle.

Tomasulo's Algorithm (Processing) Introduction to Computer Architecture Instruction Sequence lw $t0, 0 ($a0) addi $t9, $zero, 53 mult $19, Sto mflo sto $t1, 4 ($a0) lw $t1, 0 ($t1) addi $t1, $t1, -9 addi St9, Szero, 7 mult $19, $t1. St1 mflo add $t0, $t0, $t1. sw $t0, 0 ($a0) 1. For a dual-issue superscalar processor with two integer units and one load/store unit, diagram how each instruction moves through the pipeline. Indicate when each instruction reaches a given unit and when it leaves that unit. Assume that each unit can process one instruction per clock. cycle. Tomasulo's Algorithm (Processing) Introduction to Computer Architecture Instruction Sequence lw $t0, 0 ($a0) addi $t9, $zero, 53 mult $19, Sto mflo sto $t1, 4 ($a0) lw $t1, 0 ($t1) addi $t1, $t1, -9 addi St9, Szero, 7 mult $19, $t1. St1 mflo add $t0, $t0, $t1. sw $t0, 0 ($a0) 1. For a dual-issue superscalar processor with two integer units and one load/store unit, diagram how each instruction moves through the pipeline. Indicate when each instruction reaches a given unit and when it leaves that unit. Assume that each unit can process one instruction per clock. cycle

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts